Устройство для коммутации асинхронных сигналов

Иллюстрации

Показать всеРеферат

1"

t3.(О П Й АН ME

ИЗОБРЕТЕНИЯ лл7О5663

Союз Советских

Социапистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свид-ву (22) Заявлено 08.04.77 (21) 2472756/18 — 21 с присоединением заявки М (23 ) Приоритет (51)M. Кл.

Н 03 К 5/20

G 06 С 13/00 вооудеротевиный комитет

СССР ао делам изобретений н открытий (53) УДK 621 374.33 (088.8) ОпУбликовано 25 12.79. Бюллетень Рд 47

Дата опубликования описания 25.12,79 (72) Автор изобретения

Л. Ф. Хазан (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОММУТАЦИИ АСИНХРОННЬИ

СИГНАЛОВ

Изобретение относится к области устройств, предназначенных для электронной коммутации сигналов, а более точно для коммутации сигналов, асинхронно генерируемых многими независимыми источниками и поступающими на один объект, причем могут быль случаи совпа5 дения этих сигналов. Устройство может использоваться в системах программного управления, в системах сбора и обработки информации, Известно коммутирующее устройство содер10 жащее схемы сравнения и узлы блокировки, а также пороговые элементы (1).

Недостатком этого коммутирующего уст- ройства является потеря информации при

15 совпадении сигналов во времени.

Известно устройство для коммутации асинхронных сигналов, содержащее входной блок, блок определения приоритета и выходной блок, выходы и входы которого соединены соответственно с выходами устройства для коммутации асинхронных сигналов и выхода- ми блока определения приоритета, входы которого соединены с выхоцамп входного блока, 2 входы которого соединены с входами устройства для коммутации асинхронных сигналов, а управляющий вход блока определения приоритета соединен с управляющим входом устройства для коммутации асинхронных сигналов (2j.

Недостатком этого устройства является возможность потери информации в случае, если длительность последующего сигнала меньше предыдущего.

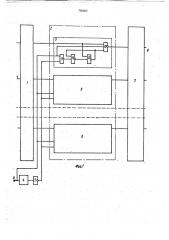

Целью изобретения является уменьшение потерь информации, Для этого в устройство для коммутации асинхронных сигналов, содержащс входной блок, блок определения приоритета и выходной блок, выходы и входы которого соединены соответственно с выходами устройства для коммутации асинхронных сигналов и выходами блока определения приоритета, входы которого соединены с выходами входного блока, входы которого соединены с входами устройства для коммутации асинхронных сигналов, а управляющий вход блока определения приорите1а соеди1тсн с управляющим входом устройства лля 4 ветствующим входом и выходом блока определения приоритета 2. Каждый узел огранИчения длительности 9 содермп три элемента

ИЛИ вЂ” HE 10, 11 и 12 и элемент И !3, первый вход элемента И 13 соединен с первым входом данного узла ограничения длительности 9, второй вход которого соединен с вторым входом элемента И 13 и первым входом первого элемента ИЛИ вЂ” НЕ 10, выход которого соединен с выходом узла ограничения длительности 9, выход элемента И 13 соединен с первым входом второго элемента

ИЛИ вЂ” HE 11,. выход и второй вход которого соединены соответственно с первым входом и выходом третьего элемента ИЛИ вЂ” НЕ !2, второй вход которого соединен с третьим входом узла ограничения длительности 9 и вторым входом первого элемента ИЛИ вЂ” НЕ 10, третий вход которого соединен с выходом третьего элемента ИЛИ вЂ” НЕ 12.

Устройство для коммутации асинхронных сигналов работает следующим образом.

При поступлении сигналов запроса от источйиков ийформации (сигналы на фиг. 2, а, б, в), первый из них (фиг. 2. а), пришедший на любой вход 7 входного блока 1 устройстl3a для коммутации асинхронных сигналов, снимает запрет с соответствующего узла ограничения длительности 9 и проходит через элемент ИЛИ вЂ” НЕ 10 на выход выходного блока

3 (сигнал на фиг, 2, д) Объект связывается с данным источником сигнала, при этом на входе 8 и, следовательно, на входах узлов ограничения длительности 9 и элемента 4 задер а<и появляется сигнал запрета от объекта (сигнал на фиг. 2 г).

Сигнал, йришедший следующим па выход блока определения приоритета 2 не проходит, так как входы узлов ограничения длительности

9 заперты сигналом логического "0" от инвертора 5 сразу после срабатывания первого узла, ограничения длительности сигнала 9.

Сигнал запроса; пришедший вторым, пройдет на соответствующий выхоК только тогда, когда пропадет сигнал запрета с объекта, то есть когда объект обработает информацию от первого источника (сигнал фиг. 2 е). При этом второй источник сигналов связывается с объектом, Ha Bblxopax блока 2 определения приоритета и элемента задержки 4 опять пбявляется сигнал запрета, и, следовательно, как описано ранее, срабатывает узел ограничения,длительности 9, соответствующий данному входу входного блока 1. Далее все происходит, как описано выше, при приходе третьего сигнала запроса (сигнал фиг. 2 в) цикл повторяется.

705663

3 коммутации асинхронных сйгналов, введены элемент задержки и инвертор, вход элемента задержки соединен с управляющим входом устройства для коммутации асинхронных сйгналов, выход элемента задержки соединен .с входом инвертора, выход которого соедп1ен с вспомогательным входом блока определении приоритета, причем вспомогательный вход блока определения приоритета соединен с первыь4и входами узлов ограничения длительности, !о второй вход и выход каждого из которых соединен с соответствующим входом и" вь!хо-! дом блока определения приоритета, а каждый узел ограничения длительности содержит три элемента ИЛИ вЂ” НЕ и элемент И, первый вход элемента И соединен с первым входом данного узла ограничения длительности, второй вход соторого соединен с вторым-входом элемента И и первым входом первого элемента

ИЛИ вЂ” НЕ, выход которого соединен с выходом 1и узла бйфйй4Чеяйя ДлнтейъйОСтЦ,-"выхоД эЛемента И соединен с первым входом второго элемента ИЛИ вЂ” НЕ, выход и второй вход которого соединены соответсгвейно с первым входом и выходом третьего элемента ИЛИ вЂ” НЕ второй !5 ВхоК которого соединен "c третьим входом узла orpàíè÷åíèÿ длительности и вторым входом первого элемента ИЛИ вЂ” НЕ, третий вход кото- фио соединен с выходом третьего элемента

ИЛИ вЂ” НЕ. ЗО

На фиг. 1. показана структурная электрическая схема устройства для коммутащщ асинхронных сигналов. На фиг. 2 приведены временные диаграммы функционирования этого устройства.

Устройство для коммутации асинхронных сигналов ; содержит входной блок 1, блок опре. деления приоритета 2 и выходной блок 3, элемент задержки 4 и инвертор 5, выходы и входы выходного блока 3 соединены соответственно с выходами 6 устройства для комму"тации асинхронных сигналов и выходами бло— ка определения приоритета 2, входы которого соединены с выходами входного блока 1, вхо- 4 ды"которого соединены с входами 7 устройст ва для коммутации асинхронных сигналов, а управляющий вход блока определения приоритета 2 соединен с управляющим входом 8 . устройствa Н кбммутации асйнхронньтх сигна- 50 лов, вход элемента задержки 4 соединен с управляющим входом 8 устройства для комму.

"таЦиЗГасинхронных сигналов, вйход элемейта задержки 4 соепинен с входом инвертора 5, выход которого соединен с вспомогательным входом блока определения приоритета 2, который соединен с первыми входами узлов ограничения длительности 9, второй вход и выход каждого из которых соединен с соот705663

Таким образом, каждый последующий источник сигналов подключается к объекту независимо от окончания сигнала запроса с предыдущего источника, и уменьшаются потери информации в случае, если длительность последую-.5 щего сигнала меньше предыдущего.

Форм ула изобретения

1. Устройство для коммутации асинхронных сигналов; содержащее входной блок, блок . определения приоритета и выходной блок, выходы и входы. которого соединены соответственно с выходами устройства для коМмута. ции асинхройных сйгналов и выходами, блока определения приоритета, входы которого соединены с выходами входного блока, входы которого соединены с входами устройства для коммутации асинхронных сигналов, а управляю- 20 щий вход блока определения приоритета соеди- нен с управляющим входом устройства для коммутации асинхронных сигналов, о т л ич а ю щ е е с я тем, что, с целью уменыпЬ ния потерь информации, в него введены эле- 25 . мент задержки и ннвертор, вход элемента задержки соединен с управляющим входом. устройства для коммутации асинхронных сигналов, выход элемента задержки соединен с входом инвертора, выход которого соединен с 30 вспомогательным входом блока определения приоритета.

2. Устройство по и. 1, о т л и ч а ьзщ е е с я тем, что блок определения приоритета содержит ряд узлов ограничения длительности, первые входы которых соединены с вспомогательным входом блока определения приоритета, а второй вход и выход каждого узла ограничения длительности соедииены соот. ветственно с соответствующим входом и выходом блока определения приоритета, а каждый узел ограничения длительности содержит три элемента ИЛИ вЂ” НЕ и элемент И, первый вход элемента И соединен с первым входом данного узла ограничения длительности, второй вход которого соединен с вторым входом элемента

И и первым входом первого элемента ИЛИ вЂ” НЕ, выход которого соединен с выходом узла ограничения длительности, выход элемента И соединен с первым входом второго элемента

ИЛИ вЂ” HE, выход и второй вход которого соединены соответственно с первым входом и выходом третьего элемента ИЛИ вЂ” НЕ, второй вход которого соединен с третьим входом узла ограничения длительности и вторым входом первого элемента ИЛИ вЂ” НБ, третий вход которого соединен с выходом третьего элемента ИЛИ вЂ” НБ,.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании Н 1394336, кл. 6 08 С 25/00, 1975.

2. Заявка Франции К 743085, кл. С08 С 13/00, 1975,(прототип).

705663 3 !! !

Составитель О. Скворцов

Техред 3. Фанта Корректор М. Вигула

Редактор Л. Гельфман. -ч

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 8054/63 Тираж 1060 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открьпий

113035, Москва, Ж вЂ” 35, Раутпскан наб., д. 4/5