Цифровой регистратор однократных длительных импульсных сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕЙ ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (ц7О5667 (61) Дополнительное к авт. саид-ву (22) Заявлено 01.06.77 (21) 2491707/18 21 с присоединением заявки РЙ (23) Приоритет (51)M. Кл.

Н 03 К 3/02

Ввударвтввнный квмнтвт

СССР ве двлам изобретений и еткрытнк

Опубликовано 25.12.79- Бюллетень М 47

Дата опубликования описания 25.12.79 (53) УЛК 621,374.32 (088.8) (72) Авторы изобретения

А. Б. Гаврилов, С. С, Караваев и В. В. Панин

Московский ордена Трудового Красного Знамени инженернофизический институт (7l) Заявитель (54) ЦИФРОВОЙ РЕГИСТРАТОР ОДНОКРАТНЫХ

ДЛИТЕЛЬНЫХ ИМПУЛЬСНЫХ СИГНАЛОВ

Изобретение относится к области измерительной техники и может быть использовано для регистрации однократных длительных импульсных сигналов с быстроизменяющейся начальной и медленноменяющейся заданной фазой сигнала, отношение медленной фазы к быстрой может быть 10 и более

Известен цифровой регистратор, содержащий запоминающее устройство, блок управления, генератор тактовых импульсов, времязадающее устройство и преобразователь аналог-код (1).

Недостатком известного устройства является то, что при записи сигналов, имеющих быструю фазу и медленную фазу, которая по времени на несколько порядков превышает быструю, фазу, требуется значительный объем памяти для запоминания значений медленной фазы сигналов

Известен также цифровой регистратор однократных длительных импульсных сигналов, содержащий запоминающее устройство, блок управления, первый генератор импульсов, датчик сигналов, времязадающее устройство, имеющее тактовый вход и вход управления, н следящий преобразователь, состоящий из .ре2 версивного счетчика, цифроаналогового преобразователя, двух элементов сравпенпя, двух элементов И и второго генератора импульсов, выход которого соединен с первымн входами элементов И, вторые входы которых соединены с выходами соответствующих элементов сравнения, выходы элементов И соединены с входами реверсивного счетчика, первые входы элементов сравнения соединены с выходом датчика сигналов, вторые входы — с выходом

1О цифроаналогового преобразователя, информационные входы которого соединены с выходами реверсивного счетчика и с первымн входамп данных запоминающего устро ства, вторые входы данных которого соединены с пнфор15 мащюнными выходами времязадающего устройства, управляющий выход которого соединен с первым входом устройства управлсния, второй вход которого соединен с управляю20

ttttt t выходом реверсивного счетчика, третий вход — с выходом первого генератора им пульсов, а первый выход — с входом записи запоминающего устройства, второй выход устройства управления соединен с тактовым вхо705667

3 .дом времязадающего устройства, а третий выход — соединен с входом управления времязадающего устройства (21.

Недостатком известпого устройства является то, что при записи сигналов, имеющих быструю и медленную фазы требуется большой объем запоминающего устройства. Так, например, при записи сигнала, отношение медленной фазы к быстрой которого составляет величину

10 и при записи медленной фазы в пяти ячейках памяти запоминающего устройства требуется объем памяти равной 5 10 слов разрядность которых равна числу разрядов реверсивного счетчика, Целью изобретения является уменыпение объема памяти запоминающего устройства.

Поставленная цель достигается тем, что в цифровом регистраторе однократных длительных импульсных сигналов, содержащем запоминающее устройство, устройство управления, первый генератор импульсов, датчик сигналов, времязадающее устройство, имеющее тактовый вход и вход управления, и следящий преобразователь, состоящий из реверсивного счетчика, цифроаналогового преобразователя, двух элементов сравнения, двух элементов И и второго генератора импульсов, выход которого соединен с первыми входами элементов

И, вторые входы которых соединены с выходами соответствующих элементов сравнения, выходы элементов И соединены с входами реверсивного счетчика, первые входы элементов сравнения соединены с выходом датчика сигналов, вторые входы — с выходом цифроаналогового преобразователя, информационные входы которого соединены с выходами реверсивного счетчика и с первыми входами данных запоминающего устройства, вторые входы данных которого соединены с информационными выходами времязадающего устройства, управляющий выход которого соединен с первым входом устройства управления, второй вход которого соединен с управляющим выходом реверсивного счетчика, третий вход — с выходом первого генератора импульсов, а первый выход — с входом записи запоминающего устройства, в следящий преобразователь введен элемент ИЛИ, дополнительный вход устройст,ва управления соединен с выходом элемента

ИЛИ, входы которого соединены с выходами элементов сравнения, второй выход устройства управления соединен с входом управления времязадающего устройства„тактовый вход которого соединен с выходом первого тактового генератора.

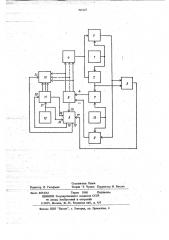

На чертеже представлена структурная электрическая схема цифрового регистратора однократных длительных импульсных сигналов.

Устройство содержит датчик сигналов 1, элементы сравнения 2, 3, цифроаналоговый преобразователь 4, элемент ИЛИ 5, устройство управления б, элементы И 7, 8, реверсивный счетчик 9, запоминающее устройство 1О, времязадающее устройство 11, генераторы импуль1 сов 12, 13, входы устройства управления 14, 15, 16, 17, выходы устройства управления 18, 19, управляющий и тактовый входы времяэа1о дающего устройства соответственно 20, 21, вход записи запоминающего устройства 22.

Устройство работает следующим образом, Код йа выходах реверсивного счетчика 9 постоянно отлеживает" входное напряжение, 15 поступающее с выхода датчика сигнала 1.

В процессе регистрации сигнала можно выделить два режима работы регистратора: режим регистрации переднего фронта и быстрых фаз сигнала (режим 1) и режим регистрации ос2о тальных фаз сигнала (режим 2). Переключение режимов осуществляет блок управления б.

Регистрация фронта сигнала начинается после того, как на вход 15 устройства управления

6 с управляющего выхода реверсивного счет25 чика 9 поступает цифровой сигнал. Этот сигнал поступает в том случае, когда реверсивный счетчик 9 накопит заданное (экспериментатором, до начала регистрации) число импульсов, что будет означать достижение сигналом с выхода

30 датчика 1 заданного уровня. После поступления на вход 15 устройства управления 6 цифрового сигнала, на вход записи 22 запоминающего устройства 10 начинают поступать с выхода 19 устройства управления б импульсы, которые следуют через равные промежутки времени Т>, задаваемые генератором 12, и ! обеспечивают запись в запоминающее устройство 10 данных с выходов реверсивного счетчика 9 и времязадающего устройства 11. После

4О записи в запоминающее устройство 10 1ч значений регистрируемого сигнала начинается отсчет времени во времязадающем устройстве

11 (дяя этого с выхода 18 устройства управления б на управляющий вход 20 времязадаю45 щего устройства 11 поступает цифровой сигнал), и в устройстве управления регистратором б происходит подключение его выхода.

19 к входу 17 (это переключение переводит регистратор во 2-й режим работы).

50 При работе регистратора в режиме 2 запись в запоминающее устройство 10 данных с выхода реверсивного счетчика о величине сигнала происходит в моменты времени срабатьвания элементов сравнения 2 или 3, при

55 этом в запоминающее устройство 10 также записьваются данные с информационных выходов времязадающего- устройства 11 о значении этого момента времени.

При поступлении с выхода датчика 1 быстрых фаз сигнала устройство управления 6 отключает свой вход 17 от своего выхода 19 и обеспечивает поступление с него на управляющий вход 22 запоминающего устройства

10 йз импульсов, следующих с периодом Тз.

После поступления импульсов вновь происходит переключение режимов работы регистратора (регистратор будет работать в режиме 2).

Окончание регистрации производится устройством управления 6 либо при переполнении запоминающего устройства 10 (сигнал перепалнения вырабатывает устройство управления) либо через промежуток временна Т после начала регистрации сигнала (в этом случае сигнал вырабатывает времязадающее устройство 11, и этот сигнал поступает с управляющего вьтхода времязадающего устройства 11 на вход 14 устройства управления 6).

Предложенное устройство позволяет значительно снизить объем запоминаемой информации по сравнению с известными цифровыми регист-. раторами.

Формула изобртения

Цифровой регистратор однократных длительных импульсных сигналов, содержащий запоминающее устройство, устройство управления, первый генератор импульсов, датчик сигналов, времязадающее устройство, имеющее тактовой вход и вход управления, и следящий преобразователь, состоящий из реверсивного, счетчика, цифроаналогового преобразователя, двух элементов сравнения, двух элементов Й и второго генератора импульсов, выход кото рого. соединен с первыми входами элементов

667

И, вторые входы которых соединены с выходами соответствующих элементов- сравнения, выходы элементов И соединены с входами реверсивного счетчика, первые входы элементов сравнения соединены с выходом датчика сигналов, вторые входы — с выходом цйфроаналогового преобразователя, информациощые входы которого соединены с выходами реверсивного счетчика и с первыми входами

10 данных запоминающего устройства, вторые входы данных которого соединены с инфор мационными выходами времязадающего устройства, управляпхций выход которого соединен с первым входом устройства управления, 15 второй вход которого соединен с управляю. щим выходом реверсивного счетчика, третий вход — с выходом первого генератора импульсов, а первый выход — с входом записи запоминающего устройства, о т л и ч а ю °

20 шийся тем, что; с целью уменьшения объема памяти запоминающего устройства, в следящий преобразователь введен элемент ИЛИ, дополнительный вход устройства управления . соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов сравнения, второй выход устройства управления соединен с входом управления времяэадаю. щего устройства, тактовый вход которого со единен с выходом первого тактового генератора., Источники информации, / . принятые во внимание при экспертизе

1, Техническое описание П53031002 к циф ровому накопителю "Сигма", блок схема

З5 П53031002 СхБ. СКБ БП AH СССР, 1968.

2. Смолов В. Б. и др. Полупроводниковые кодирующие и декодирующие преобразователи напряжения. "Энергия", 1967, с, 135, рис. 2-5а, 705667

Составитель Ранов

Техред Э. Чужик Корректор М. Вигула

Редактор Л. Гельфмаи

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 8054/63 Тираж 1060 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раугпская наб., д. 4/5