Шифратор-дешифратор позиционного п-импульсного кода

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ («>705675

Союз Советскик

Социалистических

Республик

Ф

- « »

И

Йтr

6.„,";. ;. ;" (с1)М Кл 2

Н 03 К 13/24 (61 ) Дополнительиое Ic 86T. сагид-ву— (22) Заявпеио061077 (21) 2528728/18-21 с присоединением заявки М—

Государственный коннтет

СССР но делам нэобретеннй н открытнй (23) Приоритет— (53) УДК 6 21. 3 7 4 (088.8) Опубликоваио25.12.79. Бюллетень Но 47

Дата опубликования описания 2512.79 (72) Авторы

ИЗОбрЕТЕНИя Н.М. Станишевская и Б.Л. Шарыгин (71) Заявитель (5 4 ) ШИФРАТОР-ДЕШИФРАТОР ПОЭ ИЦИОННОГО и — ИМПУЛЬСНОГО КОДА

Изобретение касается импульснОй техники и может быть применено в системах передачи информации, в част.ности, в полудуплексных системах взаимного обмена информацией:между объектами, использующих позиционйоимпульсное кодирование, при прОек-. тировании многофункциональных шифраторов-дешифраторов с текущим контролем.

Известен многофункциональный шифратор-дешифратор, содержащий логические элементы и реализующий контроль при помощи формирователя строба и двухвходовогo элемента И, что при большом количестве кодов существенно снижает надежность собственно шифратора-дешифратора и достоверность контроля (11, Известен шифратор-дешифратор позиционного и-импульсного кода, содержащий блок задержки, шифратор и дешифратор кода, входы которых подключены к отводам блока задержки, триггер, нулевой вход которого соединен с выходом дешифратора, Формирователь строба, элемент ИЛИ, выход которого связан с входом блока задержки,шифратора и дешифратора, ервый и второй элементы И и шины шифруемых, дешифруемых сигналов, контроля и селектора длительности, причем, первая подключена к входу формирователя строба, первому входу элемента ИЛИ и единичному входу триггера, вторая — ко второму вхо1ду элемента ИЛИ, третья — ко второ1О му входу первого элемента И, первый вход которого соединен с выходом триггера, четвертая; — к выходу первого элемента И (21 .

Недостатками известного устройства являются его недостаточная надежность и низкая достоверность контроля.

Цель изобретения - .повышение надежности и достоверности контро20

Для этого в шифратор-дешифратор позиционного и-импульсного кода, содержащий блок задержки, шифратор и дешифратор кода, входы которых подключены к отводам блока задержки, триггер, нулевой вход которого соецинен с выходом дешифратора, формирователь,строба, элемент ИЛИ, выход которого связан с входом блока задерж- ки шифратора и,дешифратора, первый

705675 ь10

20 и второй элементы И и шины шифруемых сигналов, дешифруемых сигналов, сигналов контроля и селектора длител ности, причем, первая подключена к входу формирователя строба, перво "%у входу элемента ИЛИ,и единичному входу триггера, вторая — ко второму входу элемента ИЛИ, третья — ко второму входу первого элемента И, первый вход которого соединен с выходом триггера, четвертая — к выходу первого элемента И, введены допол нительный блок задержки, элемент запрета, два дополнйтельных элемента И, дополнительный элемент ИЛИ, при этом выход блока задержки подключен ко входу элемента запрета, управляющий вход которого связан с первыми входами дополнительных элементой И и шиной сигнала контроля, два входа дополнительного элемента

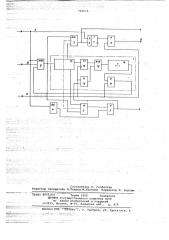

ИЛИ подсоединены соответственно к выходам элемента запрета и первого дополнительного элемента И, нторой вход которого подключен к выходу второго элемента И, причем выход дополнительного элемента ИЛИ связан с входом второго блока задержки, выход которого подключен ко второму входу второго дополнительного элемента И, а выход последнего связан с третьим входом элемента ИЛИ, нходы второго элемента И соединены соответственно с выходами шифратора и формиронателя строба., На чертеже изображена схема шифратора-дешифратора.

111ифратор-дешифратор состоит из устройства временной задержки 1, дешифратора кода 2, шифратора кода

3< .Формирователя строба 4, первого и второго элементов И 5, 6, триггера 7, схемы .элемента ИЛИ; 8, шин шифруемых сигналов 9, шин дешифруемых сигналов 10, шин сигчала контроля 11 и селектора длительности 12.

Основу шифратора-дешифратора составляет устройство временной задержки 1, которое выполнено н виде днух блоков задержки 13 и 14, элемента запрета 15, элементов И 16, 17 и элемента ИЛИ 18. Время задержки каждого блока задержки несколько больше базы кода. Вход блока задержки 13 подключен к выходу элемента ИЛИ 8, два входа которого связаны с шинами шифруемых 9 и дешифруемых 10 сигналов соответственно, а третий вход подсоединен к выходу второго элемента

И 17 устройства временной задержки. Выход первого блока задержки 13 подключен к входу элемента запрета 15, управляющий вход которого подключен к шине сигнала контроля 11 и первым входам элементов И 16, 17 устройства временной задержки. Оба входа элемента ИЛИ 18 устройства временной задержки подсоединены к выходам эле25

55 бО

65 мента запрета 15 и элемента И 19 устройства„временной задержки сооТ нетственно, второй вход которогo подключей к выходу элемента И 5.

Выход элемента ИЛИ 18 подсоединен к входу второго блока задержки 14 выход которого подключен ко второму входу элемента И 17. Все и входов шифратора 3 и дешифратора 2 подключены к соответствующим отводам блока задержки 13 ° Выход шифратора 3 связан с первым входом элемента И 5, второй вход которого подключен к выходу формирователя строба 4, вход которого связан с шиной шифруемых сигналов 9. Выход дешифратора 2 подключен к нулевому входу триггера 7, единичный вход которого связан с шиной шифруемых сигналов 9, и ныход с первым входом элемента И 6, Второй вход последней подключен к шине сигна" лов контроля 11, а выход к шине селектора длительности 12.

Устройство работает в трех режимах: шифровка, дешифровка и контроль °

В режиме шифровки по шине шифруемых сигналов 9 поступает одиночный импульс, Он устанавливает в единичное состояние триггер 7, запускает формирователь строба 4 и через элемент

ИЛИ 8 возбуждает устройство нременной задержки 1. На отводах блока задержки 13 появляются одиночные импульсы с соответствующим временем запаздывания. С отводов, предназначенных для шифровки, и одиночных импульсов поступают на шифратор 3.

На выходе последнего формируется позиционный п-импульсный код, поступающий через элемент И 5,, открытый стробом, несколько превышающим по длительности базу кода, к передатчику. Дешифратор 2 в этом режиме не срабатывает, так как на его входах имеются только одиночные импульсы, не совпадающие но нремени. Единичный потенциал с .выхода триггера 7 не проходит на селектор длительности, так как на второй вход элемента И 6 не поступает отпирающий потенциал с шины сигналов контроля 11.

Элементы И 16 и 17 закрыты по той же причине. Элемент запрета 15 открыт, что обеспечивае- связь между блоками задержки, В режиме дешифровки кодированные группы импульсон с определенными временными интервалами поступают по шине дешифруемых сигналов на один из входов элемента ИЛИ 8 и далее на нхбд первого блока задержки 13. На выходе дешифратора 2 расшифрованный импульс появится только в случае прихода соответствующего позиционного и-импульсного кода или помехи с параметрами кода, Расшифрованный импульс поступает к,потребителю информации и ус705675

Формула изобретения

50 тананлинает триггер 7 в нулевое состояние. В этом режиме на выходе шифратора появляются группы импульсов, но они не проходят на передатчик, так ка< элемент И 5 закрыт. Выхоцной сигнал триггера 7 также не поступает на шину селектора длительности 12, что обусловлено закрытым состоянием элемента И 6. В режиме контроля, который характеризуется наличием сигнала контроля на соответствующей шине 11,.импульс, поступивший на шифровку, формирует позиционный и-импульсный код на выходе элемента И 5. Этот код через элемент И 16, открытый сигналом контроля, поступает на элемент ИЛИ 18 и далее на второй блок задержки 14, время задержки которого несколько больше базы кода, Вследствие этого первый импульс кода появляется на входе элемента

И 17 после того, как процесс шифровки кода закончен и первый блок задержки 13 оТ.импульсов очищен .

Кроме того, сигнал контроля закрывает элемент запрета 15 и тем самым препятствует прохождению импульсов с первого блока задержки 13 на второй 14. 1"г- импульсный код через элемент И 17 с открытым сигналом контроля, поступает через элемент

ИЛИ 8 на вход первого блока задержки 13. дешифратор 2 производит дешиФровку кода, и его выходной сигнал переводит н нулевое состояние триггер 7, который был установлен в единичное состояние импульсом, поступившим на шифровку. В случае нормального функционирования шифраторадешифратора ныходной сигнал триггера 7 представляет собой импульс, длительность которого несколько больше удвоенной базы кода. Этот импульс через открытый сигналом конт- роля элемент И 6 поступает на селектор длительности, B случае неисправности в узлах шифратора-дешифратора, дешифронанный импульс в режиме контроля на выходе дешифратора 2 появляется значительно раньше или позже положенного момента времени или не появляется вообще, Это приводит к существенному изменению длительности выходного сигнала триггера 7, что преобразуется в сигнал неисправности селектором длительности.! !ифратор-дешифратор позиционного и-импульсного кода, содержащий блок задержки, шифратор и дешифратор кода, входы которых подключены к отводам блока задержки, триггер, нулевой вход которого соединен с выходом дешифра=ора, формирователь строба, элемент ИЛИ, выход которого связан с входом блока задержки, шифратора и дешифратора, первый и второй элементы И и шины шифруемых сигналов, дешифруемых сигналов, сигналов контроля и селектора длительности, причем первая подключена к входу формирователя строба, первому входу элемента ИЛИ и единичному входу триггера, вторая — ко второму входу элемента ИЛИ, третья — ко второму входу первого элемента И, первый вход которого соединен с выходом триггера, четвертая — к выходу первого элемента И, о т л и ч а ю щ и с я тем, что, с целью повышения надежности и достоверности контро25 ля, введены дополнительный блок за держки, элемент запрета, два дополни-тельных элемента И, дополнительный элемент ИЛИ, при этом выход блока задержки подключен ко входу элемента запрета, управляющий вход которого связан с первыми входами дополнительных элементов И и шиной сигнала контроля, дна входа дополнительного элемента ИЛИ подсоединены соответственно к выходам элемента запрет и первого дополнительного элемента И, второй нход которого под-. ключен к выходу второго элемента И, причем выход дополнительного элемента ИЛИ связан с входом второго блока задержки, выход которого подключен ко второму входу второго дополнительного элемента И, а выход последнего связан с третьим входом элемента ИЛИ, входы второго элемента И соединены соответственно с выходами шифратора и формирователя строба.

Источники информации, принятые нр внимание при экспертизе

1. Авторское свидетельство СССР

Р 465733, кл. Н 03 К 13/24, 19.12.73.

2. Авторское свидетельство СССР

Р 520702t кл. Н 03 К 13/?4, 07.06;74 (прототип) .

Составитель Л. Скобелева

Редактор Сапирштейн В.Техред М .Келемеш Корректор N . .лароши

Заказ 8055/64 Тираж 1060 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий .

113035, Москва, Ж-35, Раушская наб., д. 4/5!

Филиал ППП Патент, r. ужгОрод, ул. Проек ная, 4, Ъ