Многопороговый логический элемент

Иллюстрации

Показать всеРеферат

Союз Советскни

Сещналистнческня

Республик и "«ю E

, Л,, « „ 3««. :( (51)М. Кл.

Н 03 К 1.9/12 е (61) Дополнительное к авт. свид-ву— (22) Заявлено 05.12,77 (2!) 2548983/18-21 с присоединением заявки М—

Государственный комитет

СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 25.12.79 Бюллетень М 47 (53) УДК 821.373.

° 8 (088. 8) Дата опубликования описания 281279 (72) Авторы изобретения

И.A. Пальянов, B.И. Потапов, A П. Лысаченко и A.A. Дейлов (71) Заявитель

Омский пОлитехнический институт

/ (54) МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

3

Изобретение относится к области автоматики и вычислительной техники, в частности к пороговым логнческим элементам.

Известен пороговый логический элемент, содержащий линейный сумматор, дискриминатор (1).

Недостатком известного устройства является сложность устройства.

Известен многопорсговый логический элемент, легко реализуемый в интегральном исполнении, содержащий линейный сумматор, выполненный на резисторах, управляемый входными диодами, многопороговый дискриминатор, презназначенные для реалйзации

Функции свертки no mod 2 (2), Недостатком известного многопорогового логического элемента являют" ся его низкие функциональные возможности, не позволяющие использовать логический элемент для организации свертки по более высокому модулю, чем mod 2. Кроме того, наличие только одного выхода у известных элементов не позволяет принципиально сформировать результат свертки двоичного числа по модулю ср 2. ЗО

Целью изобретения является возможность реализации Функции свертки двоичного числа по любому модулю.

Для этого многопороговый логический элемент,,содержащий линейный сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы подключены к источнику питания и к анодам соответствующих разделительных диодов, катоды которых соединены с входом резисторного делителя, выходы которого подключены к входам соответствующих однопо роговых дискриминаторов на элементах И-НЕ, дополнительно содержит суммирующий счетчик, инверторы и двухвходовой логический .элемент ИЛИ; один вход которого соединен с выходом однопорогового дискриминатора с наинысшим порогом срабатывания, второй - с клеммой стробирующих импульсов, а выход подключен к счетному входу младшего разряда суммирующей.о счетчика, инверсные выходы раз-. рядов счетчика соединены с дополнительными входами линейного сумматора, .причт выход каждого однопорогового дискриминатора соединен с входами всех однопороговых дискрими наторов, имеющих меньший порог сра705684 батынания; выходы всех однопороговых дискриминаторов, за исключением дискриминатора с наивысшим порогом срабатынания, через инверторы подключены к выходным клеммам элемента.

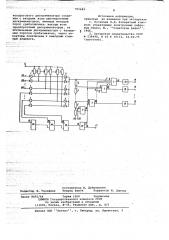

На чертеже приведена принципиальная электрическая схема многопороговoro логическorо элемента.

Многопорогоный элемент состоит из линейного сумматора, имеющего и основных и К дополнительных входов, многоразрядного дискриминатора, суммирующего счетчика, а также логических элементов HE и ИЛИ. Линейный сумматор для каждого входа содержит попарно соединенные кремниевые диоды

1 и 2, Каждая пара диодов в точках, объединяющих их аноды через резисторы 3, управляющие весовыми коэффици — ентами по,соответствующему входу, подключена к положительному полюсу источ p ника смещения 4. Катоды диодов 2 объединены и подсоединены через делитель из резисторон 5 к отрицательному полюсу источника смещения б. Многопорогоный дискриминатор состоит из <ф 25 последовательно соединенных однопороговых дискриминаторов, выполненных на элементах 7 И-НЕ. Вход 8 каждого однопорогоного дискриминатора соединен с соответствующим резистором 5 3р делителя, развязывая, тем самым, каждый последующий дискриминатор с. большим порогом срабатывания от предыдущего. Входы 9 каждого однопорогового дискРиминатора соединены с выхо-35 дами 10 однопороговых дискриминаторов, имеющих больший порог срабатывания.

Выход 10 однопорогового дискриминатора с наибольшим порогом срабатывания соединен с входом 11 логического элемента 12 ИЛИ, выход 13 которого подключен к счетному входу младшего разряда суммирующего счетчика, ныполненного на триггерах 14, Инверсные выходы 15 триггеров 14 счетчика подсоединены к дополнительным входам линей- 45 ного сумматора. Второй вход lб логического элемента 12 соединен с клеммой

17 стробирующих импульсов. Выходы 10 всех однопороговых дискриминаторов 7, кроме последнего с наибольшим порогом срабатывания, через инверторы 18 соединены с выходами 19 многопорогового логического элемента. Клеммы 20 являются основными входами линейного сумматора многопорогового логического 55 элемента. Клемма 21 подключена к положительному полюсу источника пита ния.

l.: устройство работает следующим об- бЦ разом.

Веса основных входов линейного сумматора равны весовьм характеристикам разрядов свертываемого числа. Число разрядОв счетчика К и соответстнующееб5 число дополнительных входов линейного сумматора определяется из условия и д). к щ(9 к где Ю1 - вес 1-Fo входа линейного сумматора.

Веса дополнительных входон линей-, ного сумматора, св язанных с разрядами счетчика, определяются по формуле

1-1 (й =2 q,, ц+i (f =1,2,",к)

Пороги срабатывания однопороговых дискриминаторов определяются из выражений т,=,„+, g,,", р " +„ . и+1 =1

Количество стробирующих импульсов, подаваемых на клемму 17, равно 2 — 1 „

Рассмотрим работу, например 8-ми входов ог о многопорогон oro логическ оro элемента, осуществляющего свертку по mod 3 двоичного числа. Такой элемент имеет 8 ос нов ных входов . Beса нечетных входов элемента равны единице, четных входов — двум. Количество разрядон счетчика равно 2, веса дополнительных входов линейного сумматора « р =3, -- б, Пороги срабатывания однопороговых дискриминаторов соответственно равны Т -- 10, Т =11, Т, = 12.

В исходном состоянии схемы диоды 1, связанные с выходами 15 триггеров 14 счетчика, заперты, и ток от положительного полюса источника питания 4 через резисторы 3 и открытые диоды 2 поступает н цепь последовательно включенных резисторов*5. ц+(Величина Mm -9

1=1 выходах 19 многопорогового логического элемента присутствует низкий потенциал, соответствующий уровню логического нуля . Поскольку на выходе 10 однопорогоного дискриминатора 7 с наивысшим порогом срабатывания присутствует высокий потенциал, то поступающие н клемму 17 стробирующие импульсы не вызовут изменения состояния счетчика на триггерах 14. Пусть на входы 20 многопорогового логического элемента поступил двоичный код, содержащий единицу в нечетном разрядке, а во всех остальных разрядах - нули ° При ц этом величина (.ц . с учетом

1=1 дополнительных входов примет значение, равное 10, срабатывает дискриминатор с порогом Т = 10, и на выходах 19 элемента устанавливается

705684 игналы на выходах дискр инаторов после поступле ия стробирующих импульс налы выхоэлеента ;о., Р1 (Т,=10) D2 (Т=11 D3 (Т=12 1 у

Ь

Р7i j =А.2 Вых.1

0 0 0 0

1 l

0

0 1

1 0

0 0

0

0 1

1 0

0 0

0 1

1 0

0 0

0

10

0 1

1 0

0 0

12

Формула изобретения

60 код 01, соответствуюций результату свертки по mod .3, поступившего двоичного кода. Поскольку на выходе 10 однопорогового дискриминатора 7 с наивысшим порогом срабатывания присутствует высокий потенциал, то поступающие на клемму 17 стробируюцие импульсы не вызовут изменения состояния счетчика на триггерах 14.

Пусть теперь на входы 20 многопорогового логического элемента пос- 1О тупил код, содержащий единицу в нечетном разряде и две единицы в чет ных. При этом величина Д X,„м ; с учеi=1 том дополнительных входов примет значение, равное 14, на выходе 10 15 однопорогового дискриминатора 7 с наивысшим (T =12) порогом срабаты3 вания установится низкий уровень напряжения, и первый же стробирующий импульс, поступающий на клемму gg

17, переключит младший разряд счетчика в единичное состояние. Это приМногопороговый логический элемент, 55 содержащий линейный сумматор, состоящий из входных диодов, аноды которых через соответствующие резисторы под:-:ключены к источнику питания и к ано- дам соответствуюцих разделительных диодов, катоды которых соединены с входом резисторного делителя, выходы которого подключены к входам соответствующих однопороговых дискриминаторов на элементах И-НЕ, о т л Ич а ю шийся тем, что, с целью и ведет к тому, что величина Кх;ии, Ч учетом дополнительных входов примет значение, равное 11. При этом на выходе 10 дискриминатора 7 с порогом

Т =12 устанавливается высокйй потен3 циал, и стробирующие импульсы, посту.— паюцие на клемму 17, не будут изменять состояния счетчика на триггерах 14 . На выходах диск риминаторов с порогами Т =11 и Т1 <10 установят2 ся (соответственно) низкий и высокий уровень напряжения, что приведет к Формированию на выходах 19 элемента кода 10, соответствуюцегo результату свертки по mod 3, поступившего двоичного кода.

Аналогичным образом происходит работа многопорогового логического элемента и при других комбинациях входных сигналов. Состояния элементов схемы для всевозможных значений величины %Х; >; сведены в таблицу.

И реализации Функции свертки двоичного числа по любому модулю, он дополнительно содержит суммирующий счетчик, инверторы и двухвходовой логический элемент ИЛИ, один вход которого соединен с выходом однопорогового дискриминатора с наивысшим порогом срабатывания, второй — с клеммой стробирующих импульсов, а выход подключен к счетному входу младшего разряда суммирующего счетчика, инверсные выходы разрядов которого соединены с дополнительными входами линейного сумматора, причем выход каждого од705684

Составитель Н. Дубровская

Редактор Л. Гельфман

Л Г фман Техред Фанта Корректор М, демчик

4 Заказ 8055/64 Тираж 1060 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 нопорогового дискриминатора соединен с входами всех одйопороговых дискриминаторов, имеющих меньший порог срабатывания; выходы всех однопороговых дискриминаторов, эа йсключением дискриминатора с наивысшим порогом срабатывания, через инверторы подключены к выходным клеммам элеме нта.

Источники информации, принятые во внимание при экспертизе

1. Путинцев Н.Д. Аппаратный контроль управляющих электронных цифровых машин, М., Советское радио, 1966.

2. Авторское свидетельство СССР

Р 538490, Н 03 К 19/12 24.02.75 (прототип).