Счетчик

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Сощиалистииесиих

Реслублии

<и1705688 (61) Дополнительное к авт. сеид-ву— (22) Заявлено 070177 (21) 2439214/18-21 с присоединением заявки М

{23) ПриоритетГосударственный комнтет

СССР по. делам нзобретеннй н открытий

Опубликовано 2%1279. Бюллетень HP 47 (53) УДК 621,374.. 32 (088. 8) Дате опубликования описания 25.1279

Г; С. Брайловский, И.М, Лазер и Ю.С. Крылов (73) Заявитель (8 4 ) СЧЕТЧИК щего данному в той же группе разрядов (2) .

Недос гатком этого счетчика является относительно нйэкое быстродействие. Это связано с необходимостью использоэания связи кажцого разряда со всеми последующими, что приводит к большой нагрузке на элементы и снижению быстродействия.

Цель изобретения — повышение

У быстродействия.

Для этого в: счетчик, содержащий группы разрядов, каждый из которых содержит первый и второй коммутационные триггеры:и триггер памяти, тактовые входы всех коммутационн < триггеров соединены с входом счетчи ка и вьыодами переноса лредьщущих групп, разрешающие входы всех коммутационных триггеров разрядов данной группы разрядов, кроме последнего разряда той же группы, и разрешающий вход первого ксммутационного триггера последнего разряда данной группы разрядов соединены с выходами переноса каждого разряда, предшествующего даннсму в этой группе разрядов, дополнительные входы первого коммутационного триггера

Изобретение касается вычислительной техники и автоматики и может быть использовано для счета импульсов .

Известен счетчик, содержащий группы разрядов, тактовые входы которых соединены с входом счетчика, а выход переноса каждой группы соединен с тактовыми входами разрядов.следующих групп (3.j ..

Недостатком этого счетчика является относительно . низкое быстродействие.

Известен счетчик1 содержащий группы разрядов, каждый из которых содержит первый и второй коммутационные триггеры и триггер памяти, тактовые входы всех коммутационных триггеров соединены с входом счетчика и выходами переноса предыдущих групп, разрешающие входы всех коммутационных триггеров разрядов данной группы разРядов, кроме последнего разря-. 2к да той же группы, и разрешающий вход первого коммутационного триггера последнего разряда данной группы разрядов соединены с выходами переноса каждого разряда, предшествуюь 9

/ (5 f ) М " Кл. "" " =- " - """,Ф н 03 к 23/02

705688 последнего разряда данной группы разрядов соединены с нулевыми и единичными выходами соответственно первого коммутационного триггера и триггера памяти всех разрядов кроме последнего в той же группе раз- 5 рядов, а выход переноса последнего разряда данной группы разрядов соединен с выходом переноса данной группй разрядов.

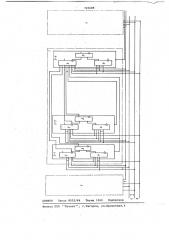

На чертеже изображена структурная схема счетчика.

Счетчик содержит группы 1 разрядов. Каждый из разрядов 2=1-2= В в группе содержит первый и второй коммутационные триггеры 3 и 4 и триггер памяти 5, тактовые входы всех коммутационных триггеров 3 и 4 соединены с входом 6 счетчика и выходами переноса 7 предыдущих групп, разрешающие входы всех коммутационных триггеров разрядов 2=1-2=п-1 данной группы разрядов, а также разрешающий вход первого коммутационного триггера 3 последнего разряда 2-п данной группы разрядов соединены с выходами переноса каждого разряда, 25 предшествующего данному в той же группе. разрядов. Дополнительные входы первого коммутационного триггера 3. последнего разряда 2-и данной группы разрядов соединены с нулевыми и 30 единичными выходами соответственно перв or о коммутационного 3 тригг ера и триггера памяти 5 каждого из разрядов 2=1-2"= и -1 той же группы разрядов, а выход переноса последнего разряда 35 данной группы раэрядон соединен с выходом переноса данной группы разрядов .

Каждая группа разрядов счетчика работает следующим образом.

Изменение состояния триггеров памяти 5 этой группы происходит по импульсам, подаваемым на вход 6 при условии, что сигналы с выходов пере- 45 носов 7 предыдущих групп равны логической единице. При выполнении этого условия происходит переключение первого триггера памяти 5 первого разряда 2 1 этой группы, если перед этим все триггеры памяти 5 этой групПы находились в нулевом логическом состоянии. По ближайшей паузе между импульсами, подаваемыми на вход б, происходит переключение второго коммутационного триггера 4 этого разряда 2=.1, При следующем выполнении условия срабатывания для этой группы разрядов переключаются первый и нторой разряды 2=1 и 2=2 этой группы и т. д. При появлении 2пМ-ого импульса, где М - коэффициент пересчета предыдущих групп раэрядон счетчика, происходит переключение всех триггеров памяти 5 данной группы разрядов в нулевое логическое состояние и формируется сигнал переноса на выходе переноса данной группы разрядов. Таким образом снижается нагрузка на выходы переносов, что обеспечивает повышение быстродействия счетчика.

Формула изобретения

Счетчик, содержащий группы разрядов, каждый из которых содержит первый и второй коммутационные триггеры и триггер памяти, тактовые входы всех коммутационных триггеров соединены с входом счетчика и выходами переноса предыдущих групп, разрешающие входы всех коммутационных триггеров разрядов данной группы разрядов, кроме последнего разряда той же груп.пы, и разрешающий вход первого коммутационного триггера последнего разряда данной группы разрядов соединены с выходами переноса каждого разряда, предшествующего данному в той же группе разрядов, о т л ич а ю шийся тем, что, с целью повышения быстродействия дополнительные входы первого коммутационного триггера последнего разряда данной группы разрядов соединены с нулеными и единичными выходами соответственно первого коммутационного триггера и триггера памяти всех разрядов, кроме последнего в той же группе разрядон, а выход переноса последнего разряда данной группы соединен с выходом переноса данной группы разрядов .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 507939, кл, Н 03 К 23)00, 260774 °

2, Авторское свидетельство СССР

Р 403069, кл. Н 03 К 21/06, 03.12,71 (прототип) .