Элемент памяти для регистра сдвига

Иллюстрации

Показать всеРеферат

пате,-; но-т ., ""- H > > G C (-- g

ОПИСАНйГ

ИЗОБРЕТЕН ИЯ

Союз Соввтских

Социалистичвских

Республик (61) Дополнительное к авт. свид-ву—

4 (22) Заявлено 05.07.78 (21) 2638181/18-24 (51) М.К .

G 11 С 19/28 с йрисоединением заявки № (23) Приоритет—

Государственный комитет

СССР

Ilo делам изобретений и открытий (53) УДК 681.327..66 (088.8) Опубликовано 30.12.79. Бюллетень №48

Дата опубликования описания 31. 12.79 (72) Авторы изобретения

П. Н. Зуб и Е. И. Семенович (71) Заявитель (54) ЭЛЕМЕНТ ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

Изобретение относится к автоматике и вычислительной технике, в частности к запоминающим элементам цифровых устройств.

Известна запоминающая ячейка для регистра сдвига, выполненная на МДП-транзисторах и состоящая из двух каскадов, каждый из которых содержит инвертор и передаточный транзистор (1). Для такой ячейки характерны невысокое быстродействие и большая мощность потребления. Обусловлено это наличием на выходе каждого каскада большой паразитной емкости, представ- ® ляющей собой емкость затвор — канал ключевого транзистора инвертора, а также наличием сквозных токов в инверторах.

Известна также ячейка памяти (2), которая характеризуется экономичностью по потребляемой мощности, поскольку отсутствуют сквозные токи. Однако быстродействие такой ячейки невысокое, так как для обеспечения нор мальной работы требуется пауза между тактовыми сигналами.

Наиболее близкой к изобретению из известных по технической сущности является ячейка памяти для регистра сдвига (3), которая содержит два элемента памяти, каж2 дый из которых включает в себя управляющий усилитель МДП-транзисторов, соединенные последовательно, и МДП-конденсатор, включенный между затвором и стоком управляющего транзистора.

Недостаток такой ячейки заключается в низком быстродействии. Причина этого— необходимость значительного увеличения емкостей истоков управляющих транзисторов по сравнению с емкостями потоков усилительных транзисторов с целью предотвращения передачи ложной логической «1», когда логический «О» следует за логической

«1». Увеличение емкостей приводит к увеличению времени заряда их, а значит, к снижению быстродействия ячейки памяти.

Цель изобретения — повышение быстродействия путем уменьшения времени заряда истоковой емкости управляющего МДПтранзистора.

Указанная цель достигается тем, что в элемент памяти для регистра сдвига, содержащий управляющий МДП-транзистор, затвор которого соединен с информационным входом элемента памяти, усилител ьный

МДП-транзистор, затвор которого соеди706880 нен со стоком управляющего МДП-транзистора и с первой тактовой шиной, сток усилительного МДП-тра нзистора соединен с истоком управл яю щего МДП-транзистора, исток усилительного МДП-транзистора с выходом элемента памяти, и вторую тактовую шину, введен разрядный МДП-транзистор, сток которого соединен с затвором управляющего МДП-транзистора, исток— с второй тактовой шиной, а затвор — со стоком усилительного МДП-транзистора.

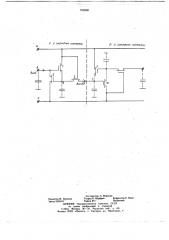

На чертеже представлена электрическая 10 схема элемента памяти.

Он содержит управляющий МДП-транзистор 1, усилительный МДП-транзистор 2, разрядный МДП-транзистор 3, тактовые шины4 и5.

Принцип работы предложенного элемента памяти удобно объяснить, рассматривая процесс сдвига информации, у которой за логической «1» следует логический «О».

При подаче на информационный вход напряжения логической «1» во время дей- щ ствия высокого потенци ала тактового сигнала на шине 4 открываются транзисторы 1 и 2 и происходит заряд узловых емкостей в точках 6 и 7. По достижении в точке 8 нап ряжения логической «1» открывается транзистор 3 и начинается разряд узловой емкости входа на шину 5, которая в это время находится под потенциалом шины нулевого потенциала. Транзистор 1 закрывается, а на узловой емкости в точке 8 сохраняется напряжение логической «1». По окончании действия высокого потенциала тактового сигнала на шине 4 закрывается транзистор 2, а на выходе элемента памяти (первого) запоминается логическая «1».

Формула изобретения

Аналогичным образом, во время действия высокого потенциала на шине 5 происходит передача напряжения логической «1» в те же точки второго элемента памяти. Открывающийся при этом транзистор 9 второго элемента памяти разряжает узловую емкость точки 7 на шину 4, находящуюся в этот момент времени под потенциалом шины нулевого потенциала.

В это же время на информационный вход элемента памяти поступает логический «О».

Управляющий транзистор второго элемента памяти предыдущей ячейки (не показан на чертеже) при этом закрыт. Поэтому узловая емкость на информационном входе

6 заряжаться не будет. Однако с помощью емкости затвор-канал усилительного транзистора второго элемента памяти предыдущей ячейки во время нарастания высокого потенциала тактового сигнала на шине 5 на узловую емкость информационного вхозо

so да первого элемента передается дополнительное напряжение, достаточное для отпирания транзистора 1. При этом происходит разряд емкости точки 8 на шину 4. Во время спада высокого потенциала тактового сигнала на шине 5 это дополнительное напряжение снимается с помощью той же емкости затвор-канал передаточного транзистора второго элемента памяти предыдущей ячейки памяти. В результате, на входе 6 сохраняется напряжение логического «О». По приходу высокого потенциала тактового сигнала на шину 4 транзистор 1 закрыт и на нулевой емкости точки 7 сохраняется напряжение логического «О». Аналогично, по приходу высокого потенциала тактового сигнала на шину 5 транзистор 10 не открывается и на выходе второго элемента тоже сохраняется логический «О».

Таким образом, благодаря введению в элемент памяти разрядного транзистора существенно повышается, по сравнению с прототипом, быстродействие, так как отпадает необходимость увеличения емкостей истоков управляющего транзистора, а следовательно время, необходимое для заряда этой емкости, уменьшается.

Элемент памяти для регистра сдвига, содержащий управляющий МДП-транзистор, затвор которого соединен с информационным входом ячейки памяти, усилительный МДП-транзистор, затвор которого соединен со стоком управляющего МДП-транзистора и с первой тактовой шиной, сток усилительного МДП-транзистора соединен с истоком управляющего МДП-транзистора, исток усилительного МДП-транзистора соединен с выходом элемента памяти, вторую тактовую шину, отличающийся тем, что, с целью повыш ения быстродействия путем уменьшения времени заряда истоковой емкости управляющего транзистора, в элемент памяти введен разрядный МДП-транзистор, сток которого соединен с затвором управляющего МДП-транзистора, исток разрядного, МДП-транзистора соединен с второй тактовой шиной, а затвор — со стоком усилительного МДП-транзистора.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3395292, кл. 307 — 221, опублик. 1968.

2. Патент США № 3575609, кл. 307 †2, опублик. 1971. 3. Патент США, № 3808458, кл. 307 — 22! опублик. 1974 (прототип) .

706880

1- и элеиенгп аамрдру

Р- и ЛГг Ячю na ЕЮ д

Составитель А. Воронин

Редактор И. Грузова Техред К. Шуфрич Корректор Е. Папп

Заказ 8236/43 Тираж 681 Подписное

ЦНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ПП П «Патент», r. Ужгород, ул. Проектная, 4