Устройство для управления блоками памяти

Иллюстрации

Показать всеРеферат

ОП ИС -"АНИЕ

ИЗОБ ЕтЕН ИЯ

Союз Соввтских

Социалистических

Республик ((() 706881

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свил-ву— (22) Заявлено 05.07.78 (2)) 2638183/18-24 с присоединением заявки №вЂ” (23) Приоритет— (5!) М, Кз.

G!1 С 29/00

Государственнь(й комитет

СССР но делам изобретений н открытий (53) УДК 681.327..6 (088.8) Опубликовано 30.12.79. Бюллетень № 48

Дата опубликования описания 31.12.79 (72) А втор изобретения

В. А. Кулагин (71 ) Заявитель (51) У(,TE ÎÃÍ.TEÇÎ ДЛЯ УГ)РАЕ)ЛЕ..НИЯ БЛОКАМИ ПАМЯТИ

Г1зобретен(ц относится к вычислительной

Teхнике, автоматикс и телемеханикс, в част,.-=;ности к устройс вам управления блоками памяти асинхронного типа с регенерацией, выполненными на базе полупроводниковых ЗУ динамического типа. Изобретение может быть использовано в вычислительной технике в устройствах ввода-вывода.

Известны устройства для управления блоками памяти (БП), выполненными на базе полупроводниковых микросхем динамического типа с периодическим восстановлением (регенерацией) записанной информации, в которых цикл их работы синхронизирован с циклом устройства управления регенерацией (1) .

Известны также устройства для управления блоками памяти, в которых цикл обращения к ЗУ выдается центральным процессором, в ответ на сигнал «занято» или «регенерация окончена» (2). При этом подача сигнала регенерации возможна только до или после окончания цикла обращения к ЗУ.

3То приводит к задержкам при включении циклов регенерации или обращения к ЗУ и соответственно к непроизводительным затратам времени активной работы ЗУ.

Эти устройства для управления блоками памяти содержат счетчик адресов регенерации, соединенный с мультиплексором адресов, генератор импульсов регенерации, триггер, подключенные к входу блока синхронизации.

Наиболее близким техническим решением к предлагаемому является устройство для

1О управления блоками памяти, содержа щее генератор импульсов регенерации, триггер состояния блока памяти, блок синхронизации, блок вывода адресов и счетчик адресов регенерации, выходом подсоединенный к одному из входов блока вывода адресов, 1 второй вход которого подключен к выходу триггера состояния блока памяти, входы которого соединены с выходами блока синхронизации соответственно (2) .

К недостатку данного устройства относится невозможность независимой от циклов обращения периодической регенерации ЗУ.

Цель изобретения — повышение быстродействия устройства.

706881

Поставленная цель достигается тем, что в устройство для управления блоками памятй въедены триггер регенерации, одновибратор, первый и второй элементы И и элемент

ИЛИ. При этом вход одновибратора соединен с выходом триггера состояния блока па» мяти и с первым входом первого элемента И, второй вход которого подключен к выходу "генератора импульсов регенерации и к первому входу триггера регенерации, второй вход которого подсоединен к входу счетчи- " ка адресов регенерации и к выходу элемента ИЛИ. Входы элемента ИЛИ.соединены с выходами элементов И соответственно, а вы хоК трйггера регенерации подключен к первому входу второго элемента И, второй вход которого подсоединен к выходу одновибратора.

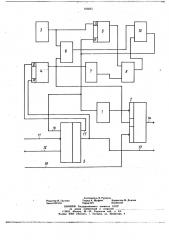

На Чертеже представлена блок-схема устройства.

Устройство содержит счетчик 1 адресов регенерации, блок 2 вывода адресов, генератор 3 ияпульсов регенерации, триггер 4 состояния блока памяти, блок 5 синхронизации, триггер 6 регенерации, одновибратор 7„ первый элемент И 8, второй элемент И 9; элемент ИЛИ 10.

Работает устройство следующим образом. . При поступлении импульсов на вход «Об ращение к БП» 11 блока 5, синхронизации и отсутствии сигнала «Занято» 12, идейтифицирующее состояние регенерации или обращение ЗУ, вырабатывается сигнал «Пуск gy

БП» 13. При этом на выходах 14 блока вы бодй "адресов выставляются адресные сигналы от ЦПУ 15, т. е. проводится нормальный цикл работы ЗУ.

Триггер 4 состояния блока памяти устанавливается на время выполнения цикла обращения в состояние низкого уровня. Импульсы регенерации с выхода генератора 3 подаются на первый элемент И 8, при условии отсутствия обращения к БП поступают на вход 16 управления «регенерация», вызы- iy вая цикл регенерации БП.

При поступлении импульсов регенерации во время выполнения цикла обращейия к

БП производится установка триггера 6 регенерации в состояние высокого уровня. В этом случае по сигналу «конец цикла БП» 17 при помощи одновибратора 7 вырабатывается импульс положительной полярности, который через элементы И 9 н ИЛИ 10 проходит на вход 16 управления «регенерация» блока 5 синхронизации, имитируя цикл регенерации ЗУ . На выходах блока 2 вывода адресов устанавливается текущее состояние выходов счетчика 1 адресов регенерации.

Сигнал обращения к БП при регенерации или предшествующем обращении запрещается сигналом «занято», выдаваемым в ЦПУ

Технико-экономический эффект состоит в том, что в предложенном устройстве сокращается длительность процессов отслеживания ЦПУ моментов возникновения циклов регенерации в БП.

Формула изобретения

Устройство для управления блоками памяти, содержащее генератор импульсов регенерации, триггер состояния блока памяти, блок синхронизации, блок вывода адресов и счетчик адресов регенерации, выход которого подключен к одному из входов блока вывода адресов, второй вход которого подключен к выходу триггера состояния блока памяти, входы которого подключены к выходам блока синхронизации соответственно, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены триггер регенерации, одновибратор, первый и второй элементы И и элемент ИЛИ, причем вход одновибратора соединен с выходом триггера состояния и с первым входом первого элемента И, второй вход которого подключен к выходу генератора импульсов регенерации и к первому входу триггера регенерации, второй вход которого подключен к входу счетчика адресов регенерации и к выходу элемента ИЛИ, входы элемента ИЛИ соединены с выходами элементов И соответственно, а выход триггера регенерации подключен к первому входу второго элемента И, второй вход которого подключен к выходу одновибратора.

Источники информации, принятые во внимание при экспертизе

1. Electronics; may 16, 1974, 45, № 10, с. 24.

2. Каталог фирмы Intel Data Catalog.

1977, с. 5 — 19...5 — 24 (прототип).

706881

Составитель В. Гуркина

Редактор И. Грузова Техред К. Шуфрич Корректор М. Демчнк

Заказ 8237/44 Тираж 681 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий ., 113035, Москва, )К вЂ” 35, Раущская наб., д. 4/5

Филиал П ПП к Патент>, г. Ужгород, ул. Проектная, 4