Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

с е;.

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

«i>708362

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 130777 (21) ? 5 )6833/16-24 с присоединением заявки М— (23) Приоритет

Опубликовано 0 5 0 18 0 Бюллетень Мо 1

Дата опубликования описания 0801.80 (51)М. К .

G 06 С 7/1р

Государственный комитет

СССР по делам нзооретеннй н открытий (53) УДК 681 335 (088.8) (72) Авторы изобретения

А.И. косолапов, О.B. Хавлин и В..П. Сенников (71) Заявитель

Ку| бышевский политехнический институт имени В.В. Куйбыщева (54) МНОЖИТЕЛЬНΠ— ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в аналоговых вычислительных и информационно-измерительных системах для выполнения операций умножения, деления и возведения в степень.

Известны множительно-делительные устройства для аналоговых сигналов, содержащие логарифмический времяимпульсный преобразователь, коммутатор входных сигналов,.генератор экспоненциального напряжения, блок управления, сумматор и фильтр среднего назначения (1), (2) .

Наиболее близким по технической сущности к предложенному изобретению является множительно-делительное устройство, содержащее последовательно соединенные коммутатор входных сигналов и логарифмический время-импульсный преобразователь, выход которого соединен с управляющим входом первого ключа, интегратор, вход которого соединен с выходом первого ключа и через второй ключ с источником опорного напряжения, информационный вход первого ключа соедин с источником опорного напряжения, выход

30 интегратора соединен со входом нульоргана, выход которого соединен с управляющими входами второго и третьего ключей, первый выход генератора экспоненциального напряжения через третий ключ соединен со входом запоминающего блока, выход которого соединен с первым входом сумматора, соответствующие выходы блока управления соединены с управляющими входами коммутатора; входных сигналов, первого ключа и генератора экспоненциального напряжения, второй выход генератора экспоненциального напряжения соединен с логарифмическим время-импульсным преобразователем(2),, Недостатком известных устройств является малое быстоодействие.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в устройство дополнительно введены четвертый, пятый и щестой ключи, выходной запоминающий блок, управляющий вход четвертого ключа соединен с выходом логарифмического время-импульсного преобразователя, а информационный вход — с выходом запоминающего блока, выход интег708362 ратора соединен со вторым входом сумматора, выход четвертого ключа соединен со входом интегратора, причем выход запоминающего блока через пятый ключ соединен со входом коммутатора входных сигналов, выход сумматора соединен через шестой ключ с (выходным запоминающим блоком, уп1равляющие входы четвертого, пятого, шестого ключей, интегратора, нульоргана соединены с соответствующими выходами блока управления.

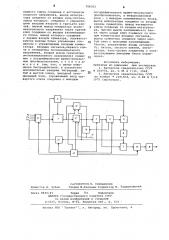

На чертеже показана схема мно>кительно-делительного устройства, которое состоит из логари*мического время-импульсного преобразователя 1, генератора экспоненциального напряжения 2, коммутатора входных сигналов 3, интегратора 4, нуль-органа

5, запоминающего блока 6, сумматора

7, выходного запоминающего блока 8, ключей 9, 10, 11, 12, 13, 14, бло- 20 ка управления 15, источника опорного напряжения 16.

Принцип действия предложенного устройства следующий. коммутатор входных сигналов 3 поочередно под- 25 ключает источники входных напряже-. ний. V«V«V> V4 запоминающего рлока 6 ко входу логарифмического время-импульсного преобразователя 1.

R первом, втором и третьем тактах формируются импульсы, пропорциональные логарифму входных напряжений

Vg, V соответственно. Эти импульсы напряжения проходят через ключ 9 и интегрируются интегратором 4.

B четвертом такте закрываются ключ 9 и открывается ключ 10, через который на вход интегратора 4 подается напряжение той же амплитуды E от источника опорного напряжения, что и н предыдущие такты, при этом напряжение на выходе интегратора 4 уменьшается. R момент когда оно становится равным нулю, срабатывает

Нуль-орган 5, который размыкает клю- 45 чи 10 и 11.

Через ключ 11 на вход запоминающего блока 6 поступает экспоненциальное напряжение от генератора экспоненциального напряжения 2. Если замы- 50 канне ключа 10 происходит в момент начала спада экспоненциального напряжения на выходе генератора экспоненциального напряжения 2, то напряжение, зафиксированное в запоминающем блоке F при размыкании ключа 11, будет пропорционально величине

Ч„Ч

V4 ъ так как справедливо следующее соотношение:

Чо Чо Ъ E (i) Сбп ++E11 Ч СО3 Ч вЂ” . =0, и

Т где Š— напряжение источника опорного напряжения; 65 амплитуда экспоненциального о напряжения;

Т вЂ” впемя периодизации; и

t — время, в течение которого открыт ключ 10; постоянная времени экспоненциального напряжения с генератора экспоненциального напряжения 2.

Из (1) споаведливо равенство ous

v ч 4.

4 2 следовательно З Чо 4

"чЯ <2

Ч e =V=uq z= о . 4 о u3

Однако полученная величина определена с некоторой погрешностью 1, для уменьшения которой в пятом, шестом, седьмом тактах преобразователь

1 внонь преобразует входные напряжения V«V< и ЧЗ, а в восьмом такте замыкается ключ 13 и напрядение с запоминающего блока 6 через коммутатор входных сигналов 3 поступает на вход логарифмического время-импульсного преобразователя 1, при этом ключ 12 замкнут, а ключи 9 и 10 разомкнуты и на выходе интегратора

4 формируется напряжение ьЧ, неличина которого пропорциональна погрешности выходного напряжения запоминающегоо блока б .

Поэтому выходное напряжение с интегратора 4 и запоминающего блока б подается на сумматор 7, выходная величина которого соответствует выполнению операции с погрешностью, (1.Ч а

Ч3 которая определяется с основном неидентичностью коэФфициента преобразования коммутатора входных сигналон 3, логари Амич еского время-импульсного преобразователя 1, интегратора 4 д я сигналов Ч.(, VZ, V3 и V4

Для исключения пульсаций на выходе устройства применен выходной запоминаю(ий блок 8, который соединен с сумматором 7 через ключ 14.

По сравнению с прототипом время преобразования уменьшено с нескольких десяткон тактов до нескольких тактов, при сохранении заданной точности. >ормула изобретения

>4ножительно-делительное устройство, содержащее последовательно соединенные коммутатор входных сигналов и логариФмический нремя- импульсный преобразователь, выход которого соединен с управляющим нходом первого ключа, интегратор, вход которого соединен с выходом первого ключа и через второй ключ с источником опорного напряжения, информационный вход

708362

15 и, и2 иу

Составитель Л. Снимщикова

Редактор Д. Зубов Техред M.Kåëåìåø Корректор Н. Задерновская

Заказ 8490/45 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 первого ключа соединен с источником опорного напряжения, выход интегратора соединен со входом нуль-органа, выход которого: соединен с управляющими входами второго и третьего клю. чей, первый выход генератора экспоненциального напряжения через третий ключ соединен со входом запоминающего блока, выход которого соединен с первым входом сумматора, соответствуюк1ие выходы блока управления соединены с управляющими входами коммутатора входных сигналов, первого ключа и генератора экспоненциального напряжения, второй выход генератора экспоненциального анапряжения соединен с логарифмИческим время-импульсным преобразователем, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в устройство дополнительно введены четвертый, пятый и шестой ключи, выходной запоминающий блок, управляющий вход чет:вертого ключа соединен с выводом логарифмического время-импульсного преобразователя, а информационный в ход — с выходом э а по ми н аюше ro блок а, выход интегратора соединен со вторым входом сумматора, выход четвертого ключа соединен со входом интегратора, причем выход запоминаюк1его блока через пятый ключ соединен со входом коммутатора входных сигналов, выход сумматора соединен через шестой ключ с выходным запоминающим блоком, упоавляющие входы четвертого, пятого, шестого ключей, интегратора, нуль-органа соединены с соответствующими выходами блока управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 264004, кл. G 06 G 7/16, 1968.

2. Авторское свидетельство ГССР по заявке "- 2101564, кл. G 06 G 7/16

1975 (прототип).