Устройство для деления

Иллюстрации

Показать всеРеферат

".Ht л

ОЛИCАНЙЕИЗОБРЕТЕНИЯ

Союз Советских! (о@иели@тиие@ких

Республик!!!! 7 I 0040 (6!) Дополнительное к авт. саид-ву (22) Заявлено 260 37Я2) ) 21 34 691/18-24

G 06 F 7/39

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет (53) УДК681. 325! (088, 8) (:)лу6ликонано 1 5.01.80, Бюллетень Ио 2

Дата опубликования описания 18,01.80 (72) Автор изобретения

Ю. Г. Бонд аре як о (5 4 ) УС ТРОЙС ТН0 ДЛЯ ДЕЛЕНИЯ

Изобретение относится к области вычислительной техники и может быть использовано, в частности, н арифметических устройствах цифровых вычислительных машин.

Известны устройства, выполняющие деление с восстанонлением остатка, беэ восстановления остатка, с использованием набора кратных делителя, с помощью преобразователя обратных величин, использующие принедение делителя к единице (1 — 5).

Такие устройства требуют большое количество аппаратуры, не достаточно совмещенное с аппаратурой, необходимой для умножения и сложения, или имеют низкое быстродействие, так как являются так тиров анными.

Наиболее близким к данному иэобрете нию яв ляется устройс тво для деления, содержащее матрицу умножения, регистры, где хранятся делимое и делитель, дешифратор для формирования начального значения у, узлы, формирующие тактовые сигналы для управления итерациями, узел, формирующий разность (2-z), где z = y>"хрезультат матрицы умножения и. узел формирования результата операции (6),30

Недостатком такого устройства является ненысокое быстродейстние, обусловленное необходимостью наличия синхронизации н устройстве, Целью изобретения яв ляетс т повышение быс тродействия .

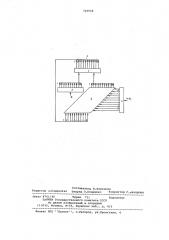

Для достижения поставленной цели в устройство для деления, содержащее регистр делимого,.регистр делителя и матрицу умножения, причем и выходов регистра делителя подключены соотнетстненно к первым и входам матрицы умножения, введен сумматор, первые и входов которого подключены к соотв е тс тв ующим п выходам ре гис тра делимого, н торые и входон су!сматора подключены к соств етств ующим и выходам матрицы умножения, а и выходов сумматора подключены соответственно ко вторым п входам матрицы умножения.

На чертеже показана структурная схема предлагаемогО устройства для деления, устройство для деления содержит су!матор 1, регистр делимого .2, матрицу умножения 3, регистр делителя 4; и разрядов регистра делимого 2 одновременно с и выходами матрицы умножения 3 подключены соответственно

710040

Р итер.

0,10101010

0,1101010100

0,1101ill1

0,1 1100001

0,11100010

О, 1 1100 010

О, 1 01 01 010

0 00000000

0,00101010

0,00110101

0,00110111

0,00111000

0,00111000

0,01000000

Формула изобретения к 2!„ входам сумматора 1, П выходов которого подключены соответственно к и входам матрицы умножения 3 (как множимое), к другим !! входам матрицы умножения 3 подключены q выходов регистра делителя 4 (как множитель).

В регистре делителя хранится дополнительный код делителя. Делитель предварительно нормализуется.

Процесс деления начинается с момента поступления делимого и дополнительного кода делителя на предварительно обнуленные регистры 2 и 4.

Количество итераций, как видно из приведенного примера, может быть и меньше и

Введение в устройство схемы сравнения может еще больше павысить быст- 40 .родействие устройства, оканчивая процесс деления при Р „ = Р,, Выстродействие йредлагкаемого устройства выше, чем прототипа, так как не затрагивается время в каждой итерации на перезапись результата с уче-. том максимальной задержки переходных процессов вычисления. Кроме того, максимально используется аппаратура, предназначенная для операций умножения, сложения, вычитания. устройство для деления, содержащее регис" ð делимого, регистр делителя и матрицу умножения, причем П выходов регистра делителя подключены соответственно к первым п входам матрицы умножения, о т л и ч а ю щ е — @) е с я тем, что, с целью повышения быПроцесс деления осуществляется по итеративному уравнению

Р,,„=а р (-Ы, где а — делимое, в — делитель, P — к-е приближение результата.

Через Ф итераций на выходе сумматора 1 формируется результат деления .

Итерационный процесс можно проследить на численном примере, P = A/Â = 0,10101010/0,11000000 стродействия, в устройство введен сумматор, первые и входов которого подключены к соответствующим п выхо- дам регистра делимого, вторые П входов сумматора подключены к соответствующим и выходам матрицы умножения, а и выходов сумматора подключены соответственно ко вторым и входам матрицы умножения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР.

Р 485447, кл. G 06 F 7/39, 1972, 2, Авторское свидетельство СССР

Р 235397, кл. G 06 F 7/52, 1966, 3. Патент США Р 3733477, кл. 235-164, 1 973.

4. Патент США Р 3633018, кл. 235-1 64, 1 972, 5. Карцев М.А, АРифметика цифровых машин. N., Наука, 1969, с. 532-536.

6. Прангишвили И,В. и др, Микроэлектроника и однородные. структуры для логических и вычислительных устройств. М,, Наука, 1967, с. 183, рис. 4.42 (прототип).

-Б)

Состав и тель В . Б ере зк ин

Редактор а.Каменская Техред 0.Андрейко Корректор Г.дазарова

Заказ 8761/49 Тираж 751 Подписное

ЦаИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4