Матричный накопитель для интегральных запоминающих устройств

Иллюстрации

Показать всеРеферат

t C 7: т тч г -X н

ОП И ИЕ

ИЗОБРЕТЕН Ия

Союз Соеетсювз

Социалистических

Республик

«1 710075

К АВТОРСКОМУ СВИДВТВЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 17.08.77 (21) 2517966/18-24 с присоединением заявки №вЂ” (23) Приоритет— (5!) M. Кл.

G I1 С 11/00

Гюсударственный комнтет

СССР на делам нзвбрвтвннй н вткрытнй (53) УДК628.327..6 (088.8) Опубликовано 15.01.80. Бюллетень № 2

Дата опубликования описания 25.01.80 (72) Авторы изобретения

А. Г. Сергеев, А. А. Орликовский, В. Н. Савенков, Б. В. Орлов и В. Н. Гладков (7!) Заявитель

Московский институт электронной техники (54) МАТРИЧНЫЛ НАКОПИТЕЛЬ ДЛЯ ИНТЕГРАЛЬНЫХ

ЗАПОМИНАЮЩИХ УСТРОЯСТВ

Изобретение относится к области микроэлектроники и может найти применение в интегральных запоминающих устройствах (ЗУ).

Известны матричные накопители для интегральных ЗУ, содержащие матрицу элементов памяти, соединенных двумя группами адресных и разрядных шин, и элементы источников тока, подключенные к адресным шинам одной из групп (!). Такие накопители обеспечивают возможность использования эффективных схем адресного и разрядного управления накопителем.

Наиболее близким техническим решением к данному изобретению является накопитель, содержащий две группы адресных и разрядных шин, в перекрестиях которых установлены элементы памяти, источник питания, подключенный через элементы согласования уровней напряжения к адресным шинам одной группы, и элементы источников тока, подключенные к адресным шинам другой группы (2). В этом устройстве благодаря протеканию токов питания элементов памяти через элементы согласования обеспечивается возможность построения экономичных схем адресных формирователей, не пот2 ребляющих мощность в режиме хранения информации.

Недостаток этого устройства заключается в сравнительно большом разбросе величины напряжения на адресной шине, обусловленном технологическим разбросом параметров элементов памяти, что приводит к снижению помехоустойчивости и разбросу динамических параметров ЗУ. Наиболее сильно этот недостаток проявляется в накопителях на элементах памяти с инверсным включением транзисторов, например инжекционных, тиристорных.

Целью изобретения является увеличение помехоустойчивости и быстродействия матричного накопителя.

Эта цель достигается тем, что матричный накопитель, содержащий две группы адресных и разрядных шин, в перекрестиях которых установлены элементы памяти, источник питания, подключенный через элементы согласования к адресным шинам одной группы, элементы источников тока, дополнительно содержит последовательно соединенные элементы памяти и согласования и опорный элемент. Дополнительные элемен710075 ты памяти и согласования подключены к источнику питания, а опорный элемент — к шине нулевого потенциала. Элементы источников тока выполнены на транзисторах, коллекторы которых подключены к соответствующим адресным шинам другой группы, эмиттеры транзисторов подключены к шине нулевого потенциала, а базы — к точке соединения опорного элемента и дополнительного элемента памяти.

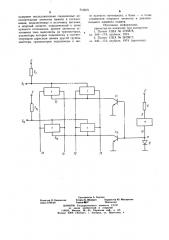

На чертеже представлена схема матричного накопителя.

Устройство содержит матрицу элементов памяти i, соединенных в и строк адресными шинами 2 (шины 2,...,2„) и адресными шинами 3 (шины 3,...,3„), элементы источников тока, выполненных на транзисторах 4 (транзисторы 4,...,4 ), элементы согласования уровня напряжения адресных шин, выполненные на резисторах 5 (резисторы 5 ...5 ), дополнительные элемент согласования, выполненный на резисторе 6, элемент памяти 7 и опорный элемент, выполненный на диоде 8. Резисторы 5 включены между источником питания Е и соответствующими шинами 2. Коллекторы транзисторов 4 подсоединены к соответствующим шинам 3, а эмиттеры соединены с шиной нулевого потенциала. Резистор 6, соединенный с источником питания Е, другим выводом подключен к адресной шине

9 элемента памяти 7. Другая адресная шина 10 элемента памяти 7 соединена в точке 11 с анодом диода 8, катод которого соединен с шиной нулевого потенциала. По разрядам элементы памяти матрицы объединяются разрядными шинами 12 и 13. Выводы элемента памяти 7, соответствующие разрядным шинам, не задействованы.

Устройство работает следующим образом.

Рассмотрим для примера работу строки с шинами 2 и 3 (другие строки идентичны ей). В режиме хранения информации транзистор 4 работает в активном режиме, и ток I>, равный коллекторному току транзистора 4, задается в шину 3 . При этом через шину 2, и резистор 5» протекает ток

I<. Через шину 9 и 10 протекают токи и 1 соответственно. Введем обозначения — =8, — =Sq,. Величины 8< и 6х опT, I

Iq ределяются параметрами структуры элементов 1 и 7. Ток 1в, протекающий через диод

8, связан с эмиттерным током 1 транзистора 4, соотношением к где величина k определяется соотношением размеров эмиттерных областей транзистора 4, и диода 8 (диод 8 выполняется на основе эмиттерного р-и-перехода транзистора). Полагая, что выполняется условйе в, =е (2) и пренебрегая базовыми токами транзисторов 4, можно получить следующее выражение для величины напряжения на шине 2

= F. — (Е-Бд — Ugq ) ° —" ° —" (3)

1(41 где Š— величина напряжения йсточника

5 питания;

U< — величина напряжения на диоде 8;

U — величина напряжения на элементе 7;

Ъ,ийв — величины резисторов 5, и 6 соответственно.

11

Как видно из уравнения (3), величина Ц, а следовательно, и величина логического перепада на шине 3, практически не зависят от параметров структуры элементов 1 и, следовательно, нечувствительны к их разбросу.

Это приводит к увеличению помехоустойчивости и быстродействия устройства.

Величина тока 1 выбирается такой, чтобы обеспечить выполнение условия (2). Если необходимо, вместо одного элемента 7 можно использовать группу элементов 7, включенных параллельно между шинами 9 и 10 (подобно включению элементов памяти в строке матрицы). Минимально допустимая величина отношения Q /1 определяется исходя из требований к стабильности величины U с учетом базовых токов транзисторов типа 4.

Как показано на чертеже, в ЗУ используется один диод 8. Если необходимо обеспечить более точное согласование характезр ристик диода 8 и транзисторов 4, можно транзисторы 4 объединять в группы, каждая из которых имеет свой диод 8, расположенный на кристалле вблизи этой группы транзисторов.

Другой возможный вариант устройства состоит в использовании цепочки диодов, последовательно включенных между источником питания Е и шиной 9, с помощью которой можно варьировать чувствительность величины Ы к отклонениям величин Е, ае UII и Uz.

Работа накопителя в режиме выборки информации осуществляется обычным для накопителей подобного типа образом.

Изобретение позволяет на 30 — 50 /ц повысить помехоустойчивость и быстродействие матричного накопителя.

Формула изобретения

Матричный накопитель для интегральных запоминающих устройств, содержащий две группы адресных и разрядных шин, в перекрестиях которых установлены элементы памяти, источник питания, подключенный через элементы согласования к адресным шинам одной группы, элементы источников тока и шину нулевого потенциала, отличающийся тем, что, с целью повышения помехоустойчивости и быстродействия накопителя, он

710075

2п

Составитель А. Сергеев

Техред К. Шуфрич Корректор Ю. Макаренко

Тираж462 Подписное

ЦН И И П И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, r. Ужгород, ул. Проектная, 4

Редактор Н. Каменская

Заказ 8768/50 содержит последовательно соединенные дополнительные элементы памяти и согласования, подключенные к источнику питания, и опорный элемент, подключенный к шине нулевого потенциала, причем элементы источников тока выполнены на транзисторах, коллекторы которых подключены к соответствующим адресным шинам другой группы, эмиттеры транзисторов подключены к шине нулевого потенциала, а базы — к точке соединения опорного элемента и дополнительного элемента памяти.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3725878, кл. 340 — 174, опублик. 1974.

2. Патент США № 3679917, кл. 340 — 174, опублик. 1974 (прототип).