Устройство для потенцирования

Иллюстрации

Показать всеРеферат

Союз Соеетскик

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 080878(2)) 2640303/18-24 с присоединением заявки ¹вЂ”

Л.

F 5/02

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет—

Опубликовано 250180 Бюллетень ¹ 3

Дата опубликования описания 30. 01. 80

681 ° 325 (088.8) (72) Авторы изобретения

О. Г. Смородинова, Г. Г. Асатиани и B. Г. Чачанидзе

О рдена Ленина институт проблем управления (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПОТЕНЦИРОВАЯИЯ ЛОГАРИФМОВ

Изобретение относится к вычисли» тельной технике и предназначено для потенцирования логарифмов последовательных двоичных кодов чисел с фик-. сированной запятой. Изобретение может найти применение в арифметикологических устройствах (АЛУ) последовательного действия с логарифмическим принципом функционирования, характеризующихся высоким быстродействием — порядка одного такта АЛУ на обработку разрядного вектора параллельно поступающих нескольких пар операндов.

Известно устройство для потенцирования логарифмов двоичных чисел, содержащее счетчик, распределитель, триггер, элемента И, ИЛИ и НЕ (1}.

Этому устройству свойственна низкая .точность вычисления, заключающаяся в том, что для некоторых двоичных кодов логарифмов чисел получаем е значение результата потенцирования от истинного отличается, начиная со второго разряда.

Наиболее близким к изобретению по технической сущности является устройство для потенцирования логарифмов двоичных чисел, содержащее рас.пределитель, вход которого подключен к шине запуска, а выходы соединены с входами элемента ИЛИ, выход которого подключен к тактирующему входу сдвигового регистра, вход сброса которого соединен с шиной установки, информационный вход — с выходом первого элемента И, а.выходы подключены к входам дешифратора, выходы которого соединены с первыми входами элементов И первой и второй групп, а также триггер, единичный выход которого не.посредственно соединен с вторыми входамк элементов И первой группы, а через элемент задержки подключен к вторым входам элементов И второй группы и к одному из входов второго элемента И, другой вход которого соединен с шиной тактирования, а выход подключен к входам сдвиговых регистров, выход каждого из которых соединен с третьим входом соответствую щего элемента И второй группы, выходы которых через первый элемент ИЛИ подключены к одному из входов сумматора, другой вход которого через второй элемент ИЛИ подключен к выходам узлов задания коэффициентов, вход каждого кз которых соединен с выходом соответствующего элемента И пер вой группы, причем третьи входы эле-.

7115б2 (ментов И первой группы подключены к выходу элемента задержки, вход которого соединен с выходом первого элемента И, один из входов которого подключен к входной шине, причем, нулевой вход триггера соединен с шиной установки, к которой подключен вход сброса счетчика (2). Недостаток известного устройства заключается в том, что вычисляемые значения результатов потенцирования для двадцатиразрядных двоичных кодов логарифмов чисел в ряде случаев от своих истинных значений отличаются с третьего разряда. целью изобретения является повыше- 5 ние точности устройства для потенцирования логарифмов °

Достигается это тем, что в устройство для потенцирования, содержащее счетчик, регистр сдвига и триггер, первые входы которых соединены с ус- 20 тановочным входом устройства, выход триггера соединен с первыми входами элементов И первОй группы и через первый элемент задержки — с первыми входами элементов И второй группы и 25 первым входом первого элемента И, через.который тактирующий вход устройства соединен с входом блока регистров сдвига, выходы которого соединены с вторыми входами соответствующих элементов И второй группы, третьи входы которых и вторые входы элементов И первой группы соединены с соответствующими выходами дешифратора, входы которого соединены с выходами регистра сдвига, выходы элементов И, второй группы через первый элемент

ИЛИ соединены с входом сумматора, выходы элементов И первой группы через соответствующие узлы задания коэффициентов соединены с входами второго элемента ИЛИ, выход которого соеди.нен с соответствующим входом сумматора, первый распределитель, вход которого соединен с управляющим входом устройства, второй элемент И, два 45 элемента ИЛИ, элемент НЕ, введены два распределителя,.три элемента ИЛИ, элемент ИЛИ-НЕ, четыре элемента И, два элемента задержки, причем, выход первого распределителя соединен 5О с входом второго распределителя, выход которого через третий элемент

ИЛИ соединен с входами второго и третьего элементов И, выход третьего элемента И соединен с вторым входом счетчика и через второй элемент задержкй — с входом третьего элемента

ИЛИ, выходы счетчика через последовательно соединенные элемент ИЛИ-НЕ,. второй элемент И и элемент НЕ соединены с входом третьего элемента И, вы- 60 ход второго элемента И через последо-. вательно соединенные третий распределитель и четвертый элемент ИЛИ соединен с входом четвертого элемента и, через который выход сумматора сое»- 65 динен с выходом устройства, перв группа выходов первого распределителя через пятый элемент ИЛИ соедине на с входом пятого элемента И, вторая группа выходов первого распределителя через шестой элемент ИЛИ соединена с входом пятого элемента ИЛИ и вторым входом регистра сдвига, группа выходов второго распределителя через седьмой элемент ИЛИ соединена с .третьим входом счетчика и через шестой элемент И вЂ” с четвертым входом счетчика, один из выходов группы второ ого распределителя соединен с втор ым входом триггера, информационный вход устройства соединен с входом шестого элемента И и через пятый элемент И с третьим входом регистра сдвига и входом третьего элемента задержки, выход которого соединен с третьими входами элементов И первой группы.

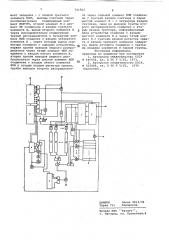

На чертеже приведена блок-схема устройства.

Устройство содержит распределители 1, 2,. 3, счетчик 4„ регистр 5 сдвига, блок б регистров сдвига, дешифратор 7, триггер 8, сумматор 9, группу узлов 10 задания коэффициентов, группу элементов И 11, группу элементов И 12, элементы ИЛИ 13-19, элементы И 20-25, элемент ИЛИ-НЕ 26, элементы 27 — 29, элемент НЕ 30.

Функционирование устройства для потенцирования логарифмов двоичных чисел осуществляется следующим образом. В исходном состоянии счетчик 4, триггер 8 и регистр 5 установлены в нулевое состояние. На первом такте по управляюшему входу на распределитель 1 подается единица. Одновременно, начиная с первого такта, на информационный вход подается сначала мантисса логарифма младшими разрядами вперед, а затем характеристика также младшими разрядами вперед. С первого по шестнадцатый такты с выхода элемента ИЛИ 17 выдается единица, которая подается на элемент И 24. В результате этого в элементе 29 запишется мантисса логарифма. Логические уровни последних четырех разрядов мантиссы логарифма заносятся в регистр 5 сдвига, так как на него с элемента ИЛИ 18 с тринадцатого по шестнадцатый такты подается единица, Вследствие этого на одном из выходов дешифратора 7 образуется единица, которая поступает на один из элементов И 11 и на один из элементов И 12.

На семнадцатом такте по сигналу с соответствующего выхода распределителя

2 триггер 8 переводится в единичное состояние, и тем самым, разблокирует элементы И 11. B результате двоичный код мантиссы логарифма из элемента

29 через выбранный элемент И 11 поступает на вход соответствующего узла

10. Единица с выхода триггера 8 че711562 рез элемент 27, время задержки которого равняется времени работы узлов

10, открывает элемент И 20, разрешая тем самым проход тактовых импульсов в блок 6. Через выбранные элементы

И 12 и элемент ИЛИ 13 информация с соответствующего регистра блока б подается на один из входов. сумматора

9, на другой вход которого через элемент ИЛИ 14 подается информация с выхода выбранного узла 10. На выходе сумматора 9 образуется мантисса двоичного числа по следующей системе уравнений: х4 — У+0,01901010110У + 0,101101010011

x =y+G G1GGQG19181y + 9 101111991191 15

x =y+6,8011101GG1Gy + 0,110801090910

x y+ 6,86l168OllO8y + 8,11ОО1О11О19О х =у+0,00101000011у + 0,116100100001 х> y+0,00011110111y + 0,110110001010 к =у+0,08018196111У + 8,119111191119 х8=У+ 0 8909101691 ly + О, 111001001100 0 с = у + 0,111619811111

<„ = l,GGGQ16ll1lly + 6,l1l980llOl8l х = 1,00010111101y + 0,119110111111 х = 1,00100100901y + 0,110100110101 х = 1,00110001000y + 0,110010011011 х1А = 1,00111110100у + 0,101111101011 х = 1,01001100101y + 9,101100100101 х„, = 1 91011011918y + 9 101001691010

Первые два члена уравнений х -х и первые члены уравнений х -х форми9 46 руются в узлах 18, а третьи члены уравнений х -х и вторые члены урав8 нений х0-х„ записаны в регистрах блока б. При этом каждому узлу 10 соответствует один из регистров блока б. 35

C семнадцатого по двадцатый такты на выходе элемента ИЛИ 19 формируется единица, которая через элемент И 25 разрешает запись характеристики логарифма в счетчик 4. На двадцать вось-® мом такте с выхода распределителя 2 единица подается на вход элемента

ИЛИ 15. Если хотя бы в одном разряде счетчика 4 записана единица, то на выходе элемента И 21 вырабатывается нулевой уровень, который через элемент НЕ 30 подается на вход элемента

И 22. Единица с выхода элемента И 22 подается на вход счетчика 4 и происходит уменьшение содержимого счетчика 4 на единицу. Единица с выхода элемента И 22 через элемент 28 на последуюцем такте подается на вход элемента ИЛИ 15. Описанный цикл повторяется до тех пор, пока не произойдет обнуление содержимого счетчика 4. И

В этом случае на выходе элемента И

21 вырабатывается единичный уровень, который запускает распределитель 3, и вырабатывается единичный уровень на выходе элемента ИЛИ 16, который Я .разблокирует элемент И 23 и на выходе устройства начинается формирование двоичного кода искомого числа.

В изобретении достигается повышение точности вычисления по сравнении у с прототипом на четыре порядка, так как в известном устройстве вычисляемые значения результатов потенцирования для шестнадцатиразрядных двоичных кодов мантисс логарифмов в ряде случаев от своих истинных значений отличаются с третьего разряда, а в заявленном — с четырнадцатого.

По предлагаемому изобретению оазработан технический проект, утвержденный Минприбором СССР. Согласно плану

Иинприбора СССР предложенное устройство для потенцирования логарифмов впервые будет внедрено на предприятии НПО Элва в 1978-1979 гг ° в составе микро-ЭВИ и перестраиваемой управляюцей логической машины. Эконо" мический эффект, который может быть получен народным хозяйством в результате использования предполагаемого изобретения при серийном производстве указанных ЭВМ в год в количестве

109 штук каждая составит около

65 тыс. руб. в год.

Формула изобретения

Устройство для потенцирования лаго рифмов содержащее счетчик, регистр сдвига и триггер, первые входы которых соединены с установочным входом устройства,выход триггера соединен с первыми входами элементов И первой группы и через первый элемент задержки— с первыми входами элементов И второй группы и первнм входом первого элемента И, через который тактирующий вход устройства соединен с входом блока регистров сдвига, выходы которого соединены с вторыми входами соответствующих элементов И второй. группы, третьи входы которых и вторые входы элементов И первой группы соединены с соответствующими выходами дешифратора, входы которого соединены с .выходами регистра сдвига, выходы элементов И второй группы через первый элемент ИЛИ соединены с входом сумматора, выходы элементов И первой группы через соответствующие узлы за" дания коэффициентов соединены с входами второго элемента ИЛИ, выход которого соединен с соответствуюцим входом сумматора, первый распределитель, вход котброго соединен с управляющим входом устройства, второй элемент И, два элемента ИЛИ, элемент НЕ, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены два распределителя, три элемента ИЛИ, элемент ИЛИ-НЕ, четыре элемента И, два элемента задержки, причем, выход первого распределителя соединен с входом второго распределителя, выход которого через третий элемент ИЛИ соединен с входами второго и третьего элементов И, выход третьего элемента И соединен с вторым входом счетчика и через второй эле711562 мент задержки — с входом третьего элемента ИЛИ, выходы счетчика через последовательно соединенные элемент ИЛ -HE второй элемент И и элемент HE соединены с входом третьего элемента И, выход второго элемента И через последовательно соединенные третий распределитель и четвертый элемент ИЛИ соединен с входом четвертого элемента И,, через который выход сумматора соединен с выходом устройства, о первая группа выходов первого распределителя через пятый элемент ИЛИ соединена с входом пятого элемента И, вторая группа выходов первого распределителя через шестой элемент ИЛИ соединена с входом пятого элемента

ИЛИ и вторым входом регистра сдвига, группа выходов второго распределителя через седьмой элемент ИЛИ соединена с третьим входом счетчика и через шестой элемент И вЂ” с четвертым входом счетчика, один из выходов группы второго распределителя соединен с вторым входом триггера, информационный вход устройства соединен с входом шестого элемента И и через пятый элемент И с третьим входом регистра сдвига и входом третьего элемента задержки, выход которого соединен с третьими входами элементов И первой группы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 446054, кл. G 06 Г 5/02, 1973.

2. Авторское свидетельство СССР, Р 523408, кл. G 06 F 5/02, 1974 (прототип).

ЦНИИП И Заказ 9013/Зб

Тираж 751 Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная,4