Ячейка однородной структуры

Иллюстрации

Показать всеРеферат

О П И С А H Â Å

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических. Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 100773,(21) 1941401/18-24 (51)М. КЛ,2 с присоединением заявки ¹ (23) Приоритет—

G 06 F 7/00

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 25.01.80. Бюллетень HP 3 (53) УДК 6 8 1. 3 25 (088. 8) Дата опубликования описания

Г. Г. Асатиани, Т„ P Давидов, В. В. Игнатущенко, Л. И. Панцхава и В. Г. Чачанидзе (72) Авторы изобретения (71) Заявитель Ордена Ленина институт проолем управления (54) ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ

Изобретение относится к автомати= ке и вычислительной технике и может найти применение для построения цифровых устройств на базе однородных микроэлектронных структур.

Известны ячейки однородной структуры, содержащие. блок входных лоГических элементов, информационные входы которых соединены с информационными входами ячейки, блок настройки базисных функций, входы которого соединены с настроечными входами ячейки, блок выходных логических элементов, блок логических функций, блок арифметических функций и блок взаимопроникновения сигналов (1).

Наиболее близким техническим решением к изобретению является ячейка однородной структуры, содержащая блок входных логических элементов, информационные входы которого соединены с инФормационными входами ячейки, а вы« ходы соединены с группами информационных входов блока логических функций, блока арифметических функций, блока регистров, блока развязки логических

Функций, управляющие входы которых соединены с соответствующими выходами блока настройки базисных функций, входы которого соединены с настроечными входами ячейки, а также блок координатной выборки, блок настройки входных логических элементов, блок совмещения автоматных и коммутационных функций и блок взаимопроникновения сигналов, регистр, элементы ИЛИНЕ, две группы элементов И, группу ,элементов HE (2).

Однако известные устройства имеют низкое быстродействие.

Целью изобретения является повышение быстродействия ячейки одиородной структуры.

Это достигается тем, что в ячейке однородной структуры, содержащей блок входных логических элементов, инфор" мационные входы которого соединены с информационными входами ячейки, выходы блока входных логических элементов соединены с группами информационных входов блока логических функций, блока арифметических функций, блока регистра,, блока развязки логических функций, управляющие входы которых соединены с соответствующими выходамй блока настройки базисных Функций, входы которого соединены с настроечными входами ячейки, блок координатной выборки, выходы которого соединены с входами блока настройки ба711563 зисных функций и через блок настройки входных логических элементов с уп-. равляющими входами блока входных логических элементон, управляющие входы блока совмещения автоматных и коммутационных функций и блока взаимопроникновения сигналов соединены с соответствующими выходами блока настройки базисных функций, выходы блока логических функций, блока арифметических функций, блока развязки логических функций, блока совмещения автоматных и коммутационных функций, блока взаимопроникновения сигналов соединены с соответствующими входами блока выходных логических элементов, входы блока настройки выходных логических элементов соединены с соответствующими входами ячейки, вход блока арифметических функций является тактирующим входом ячейки, регистр, элементы ИЛИ-НЕ, две группы элементов И, группу элементов НЕ, выходы блока входных логических элементов соединены через элементы ЯЕ группы с информационными входами блока совмещения автоматных и коммутационных, 25 функций и блока взаимопроникновения сигналов, выход блока логических функций соединен с входами блока развязки логических функций и блока совмещения автоматных и коммутационных функций, 3О выходы блока регистров через регистр соединены с первыми входами элементов ИЛИ-НЕ, соответствующие выходы блока настройки базисных функций через элементы ИЛИ-НЕ соединены З5 с первыми вХодами элементов И первой и второй групп, вторые нходы которых соединены с соответствующими выходами блока настройки базисных функций, выходы элементов 4О

И первой и второй групп соединены с соответствующими входами .блока выходных логических элементов, вы" ходы которого соединены с выходами ячейки, вход регистра соединен с тактирующим входом ячейки.,45

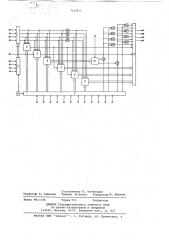

Яа чертеже представлена функциональная схема ячейки однородной структуры.

Она содержит блок 1 вхоцных логи- 5п ческих элементов;. блок 2 настройки входных логических элементов, блок 3 настройки базисных функций, блок 4 логических функций, блок 5 арифметических функций, блок 6 регистРов, блоЮ 7. развязки логических функций, блок 8 совмещения автоматных и коммутационных функций, блок 9 взаимопроникновения сигналов, регистр 10, блок

11 координатной выборки, элементы

ИЛИ-ЯЕ 12 и 13, элементы ЯЕ 14, эле- 60 менты И 15 первой группы, элементы

И 16 второй группы, блок 17 выходных логических элементов. ячейка ..однородной структуры функ" . ционирует следующим образом. 65

На выходах блока 11 координатной выборки. вырабатывается единичный логический уровень, который подключает соответствующие входы ячейки к блоку

2 настройки входных логических элементов и настроечные входы ячейки к блоку 3 настройки базисных функций, Далее осущеотвляется запись,в блок 2 кода настройки блока 1 входных логических элементов, в результате чего выбранные информационные входы соединяются со схемой ячейки, и запись в блок 3 кода настройки ячейки на реализацию базисных функций.

При выборе блока 4 логических функций ячейка реализует одну из перечисленных функций от одной до четырех переменных: И, И-НЕ, ИЛИ, ИЛИ-НЕ, равнозначности и неравнозначности.

При выборе блока 5 арифметических функций ячейка реализует либо последовательный полный сумматор для любых двух информационных входов ячейки, либо одну из перечисленных функций от одной до четырех переменных с задержкой на один такт: И, И-НЕ,,ИЛИ, ИЛИ-НЕ, равнозначности и неравнозначности. В этом случае к схеме ячейки подключается тактирующий вход.

При реализации ячейкой четырехразрядного сдвигового регистра используются блок 6 регистров, регистр 10, элементы ИЛИ-HE .12 и 13 и элементы И

15 и 16, а также тактирующий вход ячейки. Пусть ячейка реализует четырехразрядный сдниговый регистр с управлением. В этом случае блок 6 подключает к регистру 10 от одного до объединенных через дизъюкцию трех информационных входов ячейки, которые могут быть выбраны произвольно и служат в качестве информационного входа четырехразрядного сдвигового регистра, и один произвольно выбранный из оставшихся информационных входов ячейки в качестве управляющего входа четырехразрядного сдвигового регистра. При подаче единичного логического уровня на информационный вход ячейки который подключен к управляющему входу четырехразрядного сднигового регистра, осуществляется подключение тактирующего входа ячейки к регистру 10 и начинается сдвиг информации, При подаче нулевого логического уровня на указанный информационный вход ячейки тактирующий вход ячейки отключается от регистра 10 и сдвиг информации прекращается. В этом случае информация через элементы ИЛИ-ЯЕ 12, элементы И 15 и блок 17 выходных логических элементов подается на соответствующие выходы ячейки. При помощи элементон

И 15 осуществляется снятие информации с тех выходов ячейки, соответствующие информационные входы которых не были использованы в качестве информационных входов регистра 10. Если ячейка реализует четырехразрядный

711563 сдвиговый регистр без управления, блок 6 подключает к регистру 10 от одного до объединенных через дизъюкцию четырех информационных входов ячейки, которые служат в качестве информационного входа регистра 10. В этом случае тактируюций вход постоянно подключен к регистру 10, с которого информация снимается аналогичным образом через элемент ИЛИ-НЕ 13, элементы И 16 и блок 17.

При выборе блока 7 развязки логических функций ячейка реализует на

:двух произвольно выбранных выходах одну из перечисленных функций от одной до четырех переменных:.И, И-ЯЕ, ИЛИ, ИЛИ-НЕ, равнозначности и неравнозначности. При этом на двух остальных выходах ячейки реализуется либо функция ИЛИ от двух переменных, либо выдача одного произвольно выбранного переменного. 2О

При выб оре блока 8 . совмещения автоматных и коммутационных функций функционирует и блок 4. В этом случае осуществляется подключение одного произвольно выбранного информационного входа ячейки к ее произвольно выбранному выходу. Для остальных информационных входов и выходов ячейка реализует одну из перечисленных функций от одной до трех переменных: И„

И-НЕ, ИЛИ, ИЛИ-НЕ, равнозначности и неравнозначности. При выборе блока

9 взаимопроникновения сигналов ячейка реализует полный базис коммутационных функций.

Формула и зобрете ни я

Ячейка однородной структуры, содержащая блок входных логических элементов, информационные входы которого соединены с информационными входа ми ячейки, выходы блока входных логи- о ческих элементов соединены с группами информационных входов блока логических функций, блока арифметических., функций, блока регистров, блока развязки логических функций, управляющие входы которых соединены с соответствующими выходами блока настройки базисных функций, входы которого соединены с настроечными входами ячейки, блок координатной выборки, выходы которого соединены с входами блока настройки базисных функций и через. блок настройки входных логических элементов с управляющими входами блока входных логических элемен- тов, управляющие входы блока совмещения автоматных и коммутационных функций и блока взаимопроникновения сигналов соединены с соответствующими выходами блока настройки базисных функций, выходы блока логических функ. ций, блока арифметических функций, блока развязки логических функций, блока совмещения автоматных и коммутационных функций, блока взаимопроникновения сигналов соединены с соответствующими входами блока выходных логических элементов, входы блока настройки, выходных логических элементов соединены с соответствующими входами ячейки, вход блока арифметических функций является тактирующим входом ячейки, регистр, элементы ИЛИ-НЕ, две группы элементов И, группу элементов НЕ, о т л и ч а ю щ а .я с я тем, что, с целью повышения бы.cгродействия, выходы блока входных логических элементов соединены через элементы НЕ группы с информационными входами блока совмещения автоматных и коммутационных функций и блока взаимопроникновения сигналов, выход блока логических функций соединен с входами блока развязки логический функций и блока совмещения автоматных и коммутационных функций, выходы блока регистров через регистр соединены с первыми входами элементов ИЛИ вЂ , соответствующие выходы блока настройки базисных функций через элементы ИЛИЯЕ соединены с первыми входами элементов И первой и второй групп, вторые входы которых соединены с соответствующими выходами блока настройки базисных функций, выходы элементов И первой и второй групп соединены с соответствующими входами блока выходных логических элементов, выхо" ды которого соединены с выходами ячейки, вход регистра соединен с тактирующим входом ячейки.

Источники информации, принятые во внимание при экспертизе

1. Ускач N. A. Разработка и исследование многофункциональных перестраиваемых элементов и устройств на

МДП-интегральных схемах. — Автореф. дис. на соиск.учен. степени канд. техн. наук. N.: 1970.

2. Прангишвили И. В. и др. Принципы построения вычислительных устройств и методы организации вычислительных процессов на однородных структурах.

АВТ, вып. 3. Рига, Зинатне, 1972, с, 24, рис. 1 (прототип) .

711563

Заказ 9013/36

Тираж 751

Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. ужгород, ул. Проектная, 4

Составитель В. Чачанидзе

Редактор Т. Кяпокина Техред М.Петко Корректор N Шарохин