Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

«»7I1 568 е

Т "4 с ДД »

« (61) Дополнительное к авт. свид-ау (22) Заявлено 26.0777(21) 2513016/18-24 ()М. (л.2

G 06 F 7/04 с присоединением заявки М— (23} Приорытет — .

Государственный комитет

СССР по делам изобретений и открытий

Опублыковано250180 Бюллетень М 3 (53) УДК 681,325 (088. 8) Дата опубликования описания 30 . 0 1. 80 (72) Авторы изобретения

В. Г. Чачанидзе, Г. Г. Асатиани, Т. О. Кублашвили, О. Г. Смородинова и P. 3. Мирианашвили (71) Заявитель

Ордена Ленина институт проблем управления (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к области автсматики и вычислительной техники и может быть использовано при реализации технических средств автоматики и ЭВЯ для алгебраического сравнения двух синхронно поступающих в последовательном двоичном коде чисел, в которых знак содержится в первом, либо последнем разряде и сначала поступают старшие разряды.

Известны устройства для сравнения двоичных чисел, содержащие элемент неравнозначности и два элемента И-НЕ, а также R-S триггеры (11 °

К недостаткам известного устройства относятся сложность и узкие функциональные возможности, так как оно не позволяет сравнивать числа с учетом их знаков.

Наиболее близким техническим решением к предлагаемому устройству является устройство для сравнения логических чисел, содержащее элементы ИНЖ, И, ИЛИ-НЕ, ИЛИ, сумматор по модую два, триггеры, причем первая и вторая информационные шины устройства соединены со входами сумматора по модулю два, выход которого подключен к первым входам первого и второго. элементов И-НЕ, вторые входы которых. соединены с первой и второй инАормационными шинами соответственно, вы.ход первого элемента И-HE подключен ко входу установки в единичное состояние первого триггера, прямой выход которого соединен с первым входом первого элемента ИЛИ-НЕ, выход второго элемента И-НЕ подключен ко входу установки в единичное состояние второго триггера, прямой выход, которого соединен со вторым входом первого элемента ИЛИ-НЕ, выход которого подключен к третьим входам первого и второго элементов И-HE (2).

К недостаткам известного устройства относятся узкие функциональные возможности, так как оно не позволяет сравнивать числа с учетом их знаков .

Целью изобретения является повышение точности сравнения.

Это достигается тем, что в устройстве прямые выходы первого и второго триггеров соединены с первыми входами первого и второго элементов

И соответственно, первая и вторая информационные шины устройства подключены к первым входам третьего и четвертого элементов И-НЕ соответстВенно, выход третьего элемента И-,НЕ

7ll5á8 соединен со входом установки в единичное состояние третьего триггера, выход четвертого элемента И-НЕ подключен ко входу становки в единичное состояние четвертого триггера, .инверсные выходы третьего и четвертого триггеров соединены со вторыми входами первого и второго элементов

И соответственно, выходы которых подключены к о входам элеме н та ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, второй вход которого подключен к выходу первого элемента ИЛИ вЂ” HE, входы установки в нулевое с ост ояние триггеров соединены с первой шиной управления, а вторые входы третьего и четвертого 15 элементов И-НЕ подключены ко второй шине управления.

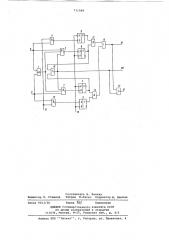

Функциональная схема устройства для сравнения двоичных чисел представлена на чертеже. 20

Устройство содержит элемент неравнозначности 1, элементы И-НЕ 2 и 3, информационные шины 4 и 5, триггеры

6-9, шину 10 управления, элементы

И-НЕ 11 и 12, элементы Й 13 и 14, элемент ИЛИ 15, элементы ИЛИ-НЕ 16 и 17, выходные шины 18, 19 и 20, шину 21 управления.

Устройство работает следующим образом.

3D

В исходном состоянии на входные шины 4 и 5 и на шины 10 и 21 управления подаются нулевые логические уровни, в результате чего триггеры

6, 7, 8 и 9 устанавливаются в нулевое состояние. При этом на выход" ной шине 20 имеем единичный логический уровень, а на выходных шинах 18 и 19 — нулевые логические уровни. На первом такте на информационные шины

4 и 5 подаются знаковые разряды ко- 40 дов сравниваемых чисел, а на шины

10 и 21 управления подаются единичные логические уровни, В результате этого элементы И 11 и 12 открываются и логические уровни знаковых разря- 45 дов запоминаются в триггерах 8 и 9.

Начиная со второго такта по и-ый такт включительно на шину 10 управления подается единичный логический уровень, а на шине 21 управления — нулевой логический уровень, т. е. элементы И 11 и 12 оказываются открытыми только на первом такте. Если в первЬм такте на шину 4 подан нулевой логический уровень (положительное число,), а на шину 5 — единичный логи- 55 ческий уровень (отрицательное число), -то триггеры 7 и 9 переходят в единичное состояние. Единичный логический уровень с единичного выхода триггера

7 через элементы ИЛИ-НЕ 16 закрывает 60 элементы И-НЕ 2 и З,,в результате чего состояние триггеров б и 7 больше не изменяется, несмотря на. то, что со второго такта на входные шины а и подаются коды сравниваемых чисел. В этом случае на выходной шине 18 имеем единичный логический уровень, а на выходных шинах 19 и 20 — нулевые логические уровни. Если в первом такте на шину 4 был подан единичный логический уровень, а на входную шину

5 — нулевой логический уровень, то триггеры б и 8 переходят в единичное состояние. Единичный логический уровень с единичного выхода триггера б через элемент ИЛИ-НЕ 16 закрывает элементы И-НЕ 2 и 3, в результате чего состояние триггеров 6 и 7 больше не изменяется, несмотря на то, что со второго такта на шины 4 и 5 подаются коды сравниваемых чисел. В этом случае на выходной шине 19 имеем единичный логический уровень, а на выходных шинах 18 и 20 — нулевые логические уровни. Пусть в первом такте на шины 4 и 5 были поданы нулевые логические уровни. В этом случае состояние триггеров 8 и 9 не изменяется. Далее, на входные шины 4 и 5 синхронно подаются последовательные .двоичные коды сравниваемых чисел, начИная со старших разрядов. Если сравниваемые числа совпадают, то в течение тактов от второго по п-ый включительно элементы И-HE 2 и 3 будут закрыты нулевым логическим уровнем с выхода элемента неравнозначности 1. Поэтому состояние триггеров б и 7 не изменяется и на выходной шине 20 имеем единичный логический уровень, а на выходных шинах 18 и

19 — нулевые логические уровни. Если сравниваемые числа не совпадают, то при первом же несовпадении логических уровней в сравниваемых разрядах триггер б либо 7 переходит в единичное состояние и блокирует элементы И-НЕ 2 и 3 ° B случае, когда

/(@opal>jfBnpl(re (A np) и (В„р ) представляют собой подаваемые собтветственно на входные шины 4 и 5 прямые коды сравниваемых чисел, то на выходной шине 18 имеем единичный логический уровень, а на выходных шинах 19 и 20 .— нулевые логические уровни. В случае когда j(A np)j» J (Впр )/, то единичный логический уровень имеем только на выходной шине 19. Пусть в первом такте на входные шины 4 и 5 поданы единичные логические уровни. В этом. случае триггеры 8 и 9 перейдут в единичное состояние. Далее устройство функционирует аналогично. При

/(А„р )1 j (В np) j единичный логический уровень имеем только на выходной шине 19, т. е. (A „p) < (Впр). При ((A лр)! < )(В Äp)(единичный логический уровень имеем только íà выходной шине 18, т. е. (А >p) ) (В яр) . Устройство для сравнения двоичных чисел осуществляет алгебраическое срав нение двух синхронно поступающих в последовательном прямом двоичном коде чисел, в которых знак содержится в rto711568 следнем разряде и сначала поступают старшие разряды аналогично описанно- му. Отличие заключается в том, что на входные шины 4 и 5 последовательные коды сравниваемых чисел синхронно подаются, начиная с первого такта, а на и-ом такте на входные шины

4 и 5 подаются знаковые разряды кодов сравниваемых чисел. Помимо того, единичный логический уровень на шину управления 21 подается только на и-ом g такте. В этом случае, кроме основной функции, устройство за (и-1) такт осуществляет сравнение по модулю двух синхронно поступающих в последовательном двоичном коде чисел, в которых сначала поступают старшие разряды. .При А >В единичный логический уровень имеем на единичном выходе триггера

6. При А (В единичный логический уровень имеем на единичном выходе триггера 7. При А = B единичный ло- 2О гический уровень имеем на .выходе элемента ИЛИ-HE 16.

Таким образом, изобретение позволяет расширить функциональнйе возможности устройства для сравнения двоич- 25 ных чисел путем реализации алгебраического сравнения двух синхронно по ступающих в последовательном прямом двоичном коде чисел, в которых знак содержится в первом либо последнем ЗО . разряде и сначала поступают старшие разряды.

Формула изобретения

Устройство для сравнения двоичных чисел, содержащее элементы И-НЕ, И, ИЛИ-НЕ, ИЛИ, сумматор по модулю два, триггеры, причем первая и вторая информационные шины устройства соединены со входами сумматора по 40 модулю два, выход которого подключен к первым входам первого и второго элементов И-НЕ, вторые входы которых соединены с первой и второй информационными шинами соответственно, выход первого. элемента И-НЕ подключен ко входу установки в единичное состояние первого триггера, прямой выход которого соединен с первым входом первого элемента ИЛИ-НЕ, выход второго элемента И-НЕ подключен ко входу установки в единичное состояние второго триггера, прямой выход .которого соединен со вторым входам первого элемента ИЛИ-НЕ, выход которого подключен к третьим входам первого и второго элементов И-HE о тл и ч а ю щ е е с я тем, что, с целью повышения точности сравнения, в устройстве прямые выходы первого и второго триггеров соединены с первыми входами первого и второго элементов И соответственно, первая и вторая информационные шины устройства подключены к первым входам третьего и четвертого элементов И-HE соответственно, выход третьего элемента

И-HE соединен со входом установки в единичное состояние третьего триггера, выход четвертого элемента И-НЕ подключен ко входу установки в единичное состояние четвертого триггера, инверсные выходы третьего и четвертого триггеров соединены со вторыми входами первого и второго элементов И соответственно, выходы которых подключены ка входам элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, второй вход которого подключен к выходу первого элемента ИЛИ-ЯЕ, входы установки в нулевое состояние триггеров соединены с первой шиной управления, а вторые входы третьего и четвертого элементов И вЂ” НЕ подключены ко второй шине управления.

Источники информации, принятые во внимание при экспертизе

1. Марри Е. Дж. Простые логические схемы для сравнения двоичных чисел. Электроника. т. 45, Р 7, И.:

Мир, 1972, с, 61 рис. 1.

2. Авторское свидетельство СССР

Р 485445, кл. G 06 F 7/04,0301.74. (прототип) .

71156В

Составитель В. Велкин

Редактор О. Стенина Техред М.Петко Корректор И, Демчик

Заказ 9013/36 тираж Я

Подписное

ЦЯИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент, г. Уигороа, ул. Проектная,