Микропрограммное устройство с контролем переходов

Иллюстрации

Показать всеРеферат

IN

Й(ф !

ОН-И САНИ Е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 1909.77 (21 ) 2527265/18-24 с присоединением заявки ¹ . (23) Приоритет

Опубликовано 250 1.80. Бюллетень ¹ 3 (51)М. К .2

G 06 F 9/14

G 06 F 11/00

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 3 (088. 8) Дата опубликования описания 25.0180 (72) Авторы изобретения

Е.A. Бабкин, Г.П. Денисова, B.À. Колосков и A.I1. Типикин

Курский политехнический институт (71) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРО тСТВО С КОНТРОЛЕМ

ПЕРЕХОДОВ

Изобретение относится к области вычислительной техники, а именно, к устройствам программного и микропрограммного управления повышенной надежности.

Известны устройства, в которых контроль хода программы и микропрограммы при естественной последовательности операций, а также при безусловных и условных переходах основан на использовании специальной избыточной информации в кодах команд и микрокоманд.

Известно устройство, содержащее запоминающее устройство программы, счетчик адреса команд, регистр команд, устройство модификации адреса схемы сравнения, схемы сверток по птсс13 (1).

В рассматриваемом аналоге контроль хода программы осуществляется поэтапно: вначале контролируется формирование адреса команды, затем производится контроль правильности обращения по адресу.

При этом для органиэации контроля правильности обращения по адресу в каждой команде предусматривается контрольный код адреса этой команды.

При обращении к запоминающему устройству (ЗУ) этот код сравнивается с контрольным кодом, образованном на счетчике команд. Необходимость в запоминании контрольных кодов адресов команд обуславливает увеличение разрядности всех слов запоминающего устройства, а для контроля формирования адреса команды необходимы дапслнтттельные схемы формирования контрольных кодов. Отмеченные факторы ведут к значительным затратам оборуцования, что является недостатком рассмотренного аналога.

Кроме того, недостатком данного устройства является невысокая способность обнаружения ошибок, нарушающих нормальный ход выполнения программы. К таким ошибкам приводят сбои в цепях выборки информации из

ЗУ, в работе адресного дешифратора, так как в результате выбирается команда, не предусмотренная выполняемым алгоритмом. Если же при этом контрольный код ошибочно считанного слова совпадает с контрольным кодом и на счетчике команд, ошибка не обнаруживается, Вероятность необнаружения подобной ошибки при исполь711573 эовании контроля по mod 3 состанля— ет О, 33.

Известно микропрограммное устройство с контролем переходов, н котором для проверки соответствия между данными и адресом, по которому их надо извлечь, формируется бит общей четности информационной и адресной части данных (2). После считывания данных бит четности сравнивается с.битом, найденным для адреса и информационной части данных. Наличие бита четности, как уже отмечалось выше, ке позволяет выявить все возможные отклонения от нормального хода программы, а запоминание контрольного кода в основной памяти увеличивает аппаратные затраты, что является недостатками рассмотренного устройства.

Отмеченные недостатки свойственны также микропрограммному устройству с контролем переходов, н котором вместе с числом н ячейку записывается, как и н предыдущем аналоге, общий контрольный код адреса и числа (3).

При считывании контрольный код адреса вычитается иэ считанного общего кода, после чего формируется контрольный код числа и сравнивается с кодом, полученным после вычитания.

Известно устройстно обнаружения )3 ошибок в работе электронно-вычислительной машины (ЭВМ), содержащее запоминающий блок, счетчик команд, регистр для запоминания контрольной

Информации считываемых из Зу команд и схему сравнения, которая осуществляет сравнение контрольных сигналов с регистра контрольной информации и счетчика команд (4) . На основании результатов сравнения производится детектирование ошибки .

4О

Общими для данного аналога и заявляемого устройства являются запоминающий блок и схема сравнения.

В приведенном аналоге контрольная информация каждой команды хранится 45 в запоминающем блоке, поэтому недостатками аналога янляется — большие затраты оборудования, вызванные ростом числа раэрядон команд и недостаточная обнаруживающая способность Я ошибки в ходе выполнения программы.

Наиболее близким Ijo технической сущности к заявляемому устройству является микропрограммное устройство с контролем переходов, содержащее память микропрограмм, регистр микрокоманд, регистр адреса, дешифратор, аппаратуру переходов, регистр адреса возврата и схемы сравнения (5) . Общими для расматриваемого и заявляемого

60 устройства являются память микропрограммы с дешифратором, объединенные в заявляемом устройстве запоминающее устройство ьякропрограмм, регистр адреса, регистр микрокоманд, аппаратура переходов, названная н предлагаемом устройстве, блок управлекия переходами и схема сравнения.

В данном устройстве контроль правильности порядка следования микрокоманд производится на основе контроля по четности, для чего все адреса заполняются разрядом четности адреса выбранного слова. Признак Четности адреса следующей микрокоманды также вводится н каждое слово микропрограммы и считывается на регистр адреса нместе с адресом.

Таким образом, и данном устройстве схема формирования признака четности заменена дополнительным кон-.ðoëüHûM разрядом и и результате каждое слово ЗУ содержит два разряда четности.

Недостаток рассмотренного устройства — большие затраты оборудования, обусловленные ростом числа разрядов микрокоманд.

Для него, как и для рассмотренных выше, хаоактерка невысокая обнаруживающая способность схем контроля.

При ошибочной работе дешифратора адреса, а также при ошибке н передаче или формировании адреса следующей микрокоманды на регистре адреса возможно ошибочное считывание из памяти микропрограмм слова, признак четности адреса каждого из которых совпадает с признаком четности на регитре адреса. Такая ошибка не обнаруживается, хотя порядок следования микрокомакд нарушается, а вероятность необнаружения ошибки составляет 0,5.

Для всех известных устрой стн Характерны недостаточная обнаруживающая способность отклонений от нормального хода программы, а также значительные затраты оборудования, необходимые для обнаружения этих отклонений.

Это объясняется тем, что н качестве критерия правильности хода программы используется совпадение контрольных кодов адресов слов программы.

В описанных выше известных устройствах используются контрольные коды по

mod 3 и mod 2, которые ке позволяют выявить нсе возможные нарушения последовательности выполнения команд и микрокоманд, так как для ких характерны высокие вероятности пропуска ошибки, составляющие 0,33 и 0,5 соответственно.

Использование кодон с большей обнаруживающей способностью приведет в известных устройствах к повышению уровня избыточности, так как возрастает число запоминаемых контрольных разрядов. Добавление разрядов ведет к росту оборудования разрядных цепей ЗУ и регистра микрокоманд.

Кроме того, для формирования контрольного кода адреса следующей микрокоманды более сложные схема формирования контрольных кодов, которые н частных случаях, например, в прототипе, могут быть заменены дополнительнымии к онтрол ьными разрядами в ЗУ

Следовательно, повышение способности обнаружения отклонений кода программы от нормального в известных устройствах связано с существенной перестройкой всего устройства и большими затратами емкости памяти.

Целью изобретения является повышение эффективности контроля и сокраще- 1О ние оборудования.

Поставленная цель достигается тем, что микропрограммное устройство с контролем переходов, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, блок сравнения 1 и блок управлени я пере ходами, причем выход блока управления переходами соединен с первым входом регистра адреса, выход которого соединен с блоком памяти микрокоманд, выход бло- Я ка памяти микрокоманд соединен со входом регистра микрокоманд, первый и второй выходы которого соединены соответственно с первым входом блока сравнения и вторым входом регистра адреса, выход блока сравнения является выходом устройства, устройство дополнительно содержит сдвигающий регистр, вь;хсд которого соединен со вторым входом блока сравнения, выход блока сравнения соединен с установочным входом сдвигающего регистра, информационный вход которого соединен с выходом блока управления переход.-..-и .

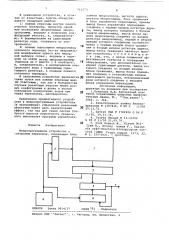

Схема микропрограммного устройст— ва с контролем переходов приведена на чертеже. В устройство входят блок 1 памяти микрокоманд, регистр адреса 2, регистр 3 микрокоманд, блок 4 управления переходами; блок сравнения 5 и сдвигающий .регистр 6, 40 выход 7.

Для контроля правильности следования микрокоманд в микропрограмму введены специальные контрольные микрокоманды, содержащие контрольную 4$ информацию для соответствующих участков исходной микропрограммы. Контрольная информация формируется для имеющейся микропрограммы с учетом порядка .следования микрокоманд условно- щ

ro и безусловного перехода на различных участках микропрограммы.

Так как каждый участок микропрограммы характеризуется определeííoé последовательностью значений опрашиваемых логических условий и микрокоманд безусловного перехода, то контрольный код участка представляет coáîrr последовательность нулей и единиц, где

1 соответствует единичному значению логического условия, а Π— нулевому

60 значению логического условия и безусловному переходу.

Максимальная величина участка микропрограммы, .охваченного контрольным словом, ограничивается лишь раз- 65 рядностью слов ЗУ микропрограмм, а минимальная величина — допустимыми пределами увеличения числа избыточных слов в запоминающей устройстве.

Устройство работает следующим образом.

По адресу, записанному на реги=тре адреса 2 из блока 1 выбирается на регистр 3 очередная микрокоманда, Адресная часть считанной микрокоманды передается из регистра 3 на регистр адреса 2. Если считана микрокоманда условного перехода, то значение соответствующего логического условия из блока 4 управления переходами передается на второй вход регистра адреса 2, где мод1.фицируется определенная позиция адреса следующей микрскоманды. Значение опрашиваемого логического условия (1 или О) поступает также на информационный вход сдвигающего регистра 6. При этом одновременно со сдвигом производится запись значения логического условия в первый разряд регистра 6.

Нумераци я разрядов прои э водится слева направо.

Если считана микрокоманда безусловного перехода„ то с выхода блока

4 на регистр адреса 2 и сдвигающий регистр б никакой информации не передается. При этом в сдьигающем регистре б производится сдвиг информации с записью нуля в первый разряд.

В случае, если считана контрольная микроксманда, блок сравнения 5 производит сравнение содержимого сдвигаюшего регистра б с контрольным кодом, записанным на регистре микрокоманд 3. Если при выполнении микропрограммы от предыдущей контрольной микрокоманды все переходы были произведены верно, то на выходе 7 блока сравнения 5 появляется сигнал отсутствия ошибки, свидетельствующий о совпадении содержимого сдвигающего регистра б и считанного контрольного кода. Сигнал отсутствия ошибки с выхода схемы сравнения 5 поступает на установочный вход сдвигающего регистра б и устанавливает его в 1.

После этого производится считывание очередной микрокоманды и сдвигающий регистр заполняется соответствующей выполняемой микрокоманде контрольной информацией.

Если при выполнении какого-либо участка микропрограммы будет осуществлен хотя бы один неправильный условный или безусловный переход, то .эта ошибка обнаруживается при считывании контрольного слова в конце участка, так как в этом случае содержимое сдвигающего регистра б не совпадает со считанным контрольным кодом.

711573

Формула изобретения

ПЯИИПИ Заказ 9014/37 ираж 751 Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

В заявляемом устройстве, в отличие от известных, всегда обнаруживаются следующие ошибки:

1) ложные переходы внутри одного участка (воэвраты, пропуски одной или нескольких микрокоманд) микропрограммы, ведущие к изменению конфигурации участка, а, следовательно, и формированию на сдвигающем регистре кода, отличного от контрольного; 10

2) ложные выполнения микрокоманд условного перехода (из-эа неправильной модификации адреса или неверной выборки слова), ведущие к переходу на новую ветвь микропрограммы (переход по 0 вместо 1 и наоборот), а, следовательно, к несовпадению контрольного кода с содержимым сдвигающего регистра, в позиции ложного условного перехода, B заявляемом устройстве выявляются Щ также почти все ложные переходы меж,ду участками, так как в большинстве. случаев различные участки имеют разную конфигурацию и длину и полное совпадение контрольных кодов при 25 таких перескоках, маловероятно.

Применение предлагаемого устройства в микропрограммных устройствах (и программных) управления реальными объектами может дать значительный эффект, так как для таких систем требуется высокая вероятность правильного выполнения программ управления.

Микропрограммное устройство с контролем переходов, содержащее блок. памяти микрокоманд, регистр адреса, регистр микрокоманд, блок сравнения и блок управления переходами, причем выход блока управления переходами соединен с первым входом регистра адреса, выход которого соединен с блоком памяти микрокоманд, выход блока памяти микрокоманд соединен со входом регистра микрокоманд, первый и второй выходы которого соединены соответственно с первым входом блока сравнения и вторым входом регистра адреса, выход блока сравнения является выходом устройства, о т л и ч а ю щ е ес я тем, что, с целью повышения эф-. фективности контроля и сокращения оборудования, оно дополнительно содержит сдвигающий регистр, выход которого соединен со вторым входом блока сравнения, выход блока сравнения соединен с установочным входом сдвигающего регистра, информационный вход которого соединен с выходом блока управления переходами.

Источники информации, принятые во внимание при экспертизе

1.Пужинцев Н.Д. Аппаратный контроль управляющих цифровых вычислительных машин, М., Сов.радио, 1966, с. 364.

2. Акцептованная заявка Великобритании 9 1297836, G 06 F 11/08

29.11.72.

3. Патент США 9 3789204 G 06 F

11/10, 29.01.74.

4. Заявка Японии 9 51-33702

G F 11/00 21.09.76.

5. Cook Robert W. Sisson Wil—

11am H.i Storey bomas F, Design

ofa ве(Е-cheching microprogrom соп го6 дЕЕЕ Trans Comput 1973., 22, М 3, 255-262), — прототип.