Программируемое постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

!

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 711634

Союз Советскик

Социалистическик

Реслублик (61) Дополнительное к авт. свид-ву (22)Заявлено 03.10.78 (21) 2669975/18 24 с присоединением заявки М (51) М. Кл.

G 11 С 17/00 (23) Приоритет

9вудерстееииьй квинтет

СССР

- ве ленам изобретений и етериткЯ

Опубликовано 25.01.80, Бюллетень .% 3

Дата опубликования описания 28.01.80 (53) УДК 681.327..6(088.8) (72) Авторы изобретения

Ю. И. Щетинин, А. Н. Иванов и В. П. Ачдреев (7I) Заявитель (54) ПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮШЕЕ

УСТРОЙСТВО

Изобретение относится к области пос-тоянных запоминающих устройств (ПЗУ) .

Известны ПЗУ, содержащие адресные формирователи и дешифраторы, накопитель с адресными и разрядными шинами, разрядные формирователи jl).

Наиболее близким техническим решением к предлагаемому является ПЗУ, в котором с пелью повышения надежности содержатся дополнительные запоминающие элементы и дополнительные шины управления . (2).

Недостатком известных устройств является отсутствие возможности функпионального контроля электроники обрамле-. ния накопителя без кодирования информации в основном поле накопителя.,Панное условие является обязательным при контроле однократно электрически программируемых ПЗУ, так как явления, происхо- 2О дящие в его элементах памяти при записи, необратимы.

Белью изобретения является повышение надежности устройства.

Это достигается тем, что в программируемое постоянное запоминающее устройство, содержащее адресные формирователи и формирователи разрешения выборки, соответственно подключенные через дешифратор и разрядные формирователи к накопителю, разрядные и адресные шины, введены дополнительные адресный и разрядный формирователи, дополнительные элементы памяти, дополнительные разряд» ная и адресная шины, одни из дополнительных элементов памяти подключены к соответствующим разрядным шинам нако пителя и дополнительной адресной шине соединенной с одним из выходов дополнительного адресного формирователя, дну гой выход которого соединен с блокирУто щим входом дешифратора, другие дополни» тельные элементы памяти подключены K соответсгвующим адресным шинам и дополнительной разрядной шине, подключенной через дополнительный разрядный фор- мирователь к формирователю разрешения выборки.

711634

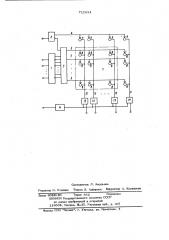

На. чертеже представлена структурная схема устройства.

ПЗУ содержит адресные формировате— ли 1, дополнительный адресный формирователь 2, дешифратор 3, формирователь

4 разрешения выборки, адресные шины

5, дополнительную адресную шину 6, накопитель 7 с основными запоминающими элементами 8, дополнительнь-..е элементы памяти 9 и 1 О, дополнительную pBGpHgH щину 11, разрядные шины 12, разрядные формирователи 13, дополнительный разрядный формирователь 14.

Для контроля электроники обрамле- ния накопитель ПЗУ необходимо и достаточно убедиться в отсутствии замыканий и обрывов адресных и разрядных шин 5 и 12, так как отказ любого компонента электроники обрамления можно интерпретировать как обрыв или замыкание соответствующей шины. Для контроля целостности и незамкнутости шин используются дополнительные запоминающие элементы 9 и 10 контрольной адресной шины

6 и контрольной разрядной шины 11. Лля контроля разрядных шин 12 необходимо производить последовательную запись в каждый разряд накопителя (включая контрольный) по контрольному адресу в элементы 9 (включена контрольная адресная шина 6, все адресные шины 5 отключены вне зависимости от входного адресного кода), причем после каждой записи необходимо производить считывание и контроль по контрольному адресу с целью проверки правильности записи по остальным разрядам. Для контроля адресных шин 5 необходимо последсвательно производить запись в контрольный разряд в элементы 10 по каждому адресу ПЗУ (за исключением контрольного адреса), причем после каждой записи необходимо производить считывание и контроль по всем адресам для проверки правильности записи по данному и отсутствия записи по остальным адресам. Нля контроля целостности запоминающих элементов 8 необходимо произвести считывание и контроль содержимого основного накопителя 7.

Формула изобретения

Программируемое постоянное запоминающее устройство, содержащее адресные формирователи и формирователи разрешения выборки, соответственно подключенные через дешифратор и разрядные формирователи к накопителю, разрядные и адресныешины, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительные адресный и разрядный формирователи, дополнительные элементы памяти, дополнительные разрядную и адресную шины, одни из дополнительных элементов памяти подключены к соответствующим разрядным шинам накопителя и дополнительной адресной шине, соединенной с одним из выходов дополнительного адресного формирователя; другой выход которого соединен с блокирующим входом дешифратора, другие дополнительные элементы памяти подключены к соответствующим адресным шинам и дополнительной разрядной шине, подключенной через дополнительный разрядный формирователь к формирователю разрешения выборки.

Источники и1;форма щпт, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

4 Л 568081, кл. 6 11 С 17/00, G 11 С 29/00, 03.02.75.

2. Авторское свидетельство СССР № 595793, кл. G 11 С 17/00, 29.11.76 (прототип) .

711634

Составитель Л, Амусьева

Редактор О. Стенина Техред Л. Алферова. Корректор О. Ковинская

Заказ 9022/40 Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открьггий

113036,-Москва, Ж-35, Раушская наб., p. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4