Многоканальный преобразователь частоты в код

Иллюстрации

Показать всеРеферат

Сонзз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 28.08.78 (21) 2659830/18-21 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.01.80. Бюллетень № 4 (45) Дата опубликования описания 30.01.80 (51) М. К .

Н ОЗК 13/02

Государственный комитет

СССР (53) УДК 621.372 (088.8) ио делам изобретений и открытий (72) Авторы изобретения

В. П. Жабеев, В. И. Королькевич и В. А. Кротевич (71) Заявитсль

Киевское проектно-конструкторское бюро автоматизированных систем управления (54) МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

ЧАСТОТЫ В КОД

Изобретение относится к области преобразования и кодирования информации и может быть использовано в многоканальных информационно-измерительных системах с автоматической обработкой данных на ЦВМ.

Известны многоканальные преобразователи, применяемые в системах испытаний сложных технологических объектов для преобразования частоты информационного сигнала в код (1).

Их недостаток — сложная структура.

Из известных многоканальных преобразователей наиболее близким к изобретению по технической сущности является многоканальный преобразователь частоты в код, каждый из каналов которого содержит логический элемент ЗАПРЕТ, первый вход которого соединен с источником преобразуемого сигнала, а выход и второй вход — соответственно с входом и выходом пересчетного устройства, а также блок установки коэффициента пересчета, блок памяти, измерительный счетчик, триггер и два генератора одиночных импульсов, а также логический элемент И и блок управления (2).

К недостаткам известного устройства следует отнести сложность структуры. ° . 1 г

712953

Целью изобретения является упрощение структуры преобразователя и повышение его надежности.

Предлагаемый многоканальный преобра5 зователь частоты в код содержит в каждом из каналов логический элемент ЗАПРЕТ, первый вход которого соединен с источником преобразуемого сигнала, а выход и второй вход — соответственно с входом и

10 выходом пересчетного устройства, второй вход которого связан с блоком установки коэффициента пересчета, триггер, соединенный по входу с выходом элемента ЗАПРЕТ, а по выходу — с первым входом гене15 ратора одиночных импульсов. При этом выходы пересчетных устройств всех каналов соединены через многовходовый логический элемент И с блоком управления, выход которого связан с вторыми входами

20 триггеров, третьими входами пересчетных устройств п первым входом измерительного счетчика, а его второй вход — с первым выходом генератора калиброванной частоты, второй выход которого объединяет вто25 рые входы генераторов одиночных импульсов, выходами подключенных к информационным входам блока памяти. Особенностью предлагаемого преобразователя является

712953

30

65 то, что в нем выходы генераторов одиночных импульсов через логический элемент ИЛИ подключены к входу записи блока памяти, адресные входы которого соединены с выходами измерительного счетчика, а выход (п — 1)-го разряда каждого пересчетного устройства соединен с входом соответствующего триггера.

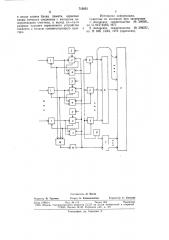

На чертеже представлена блок-схема многоканального преобразователя частоты в код.

Многоканальный преобразователь содержит в каждом канале элемент ЗАПРЕТ 1, пересчетное устройство 2, блок 3 установки коэффициента пересчета, триггер 4 начала отсчета и генератор 5 одиночных импульсов.

Общими элементами для всех каналов преобразователя являются генератор б калиброванной частоты, измерительный счетчик 7, логический элемент ИЛИ 8, блок 9 памяти, легический элемент И 10, блок 11 управления.

Устройство работает следующим образом.

Перед началом измерений, в зависимости от диапазона частот входных сигналов и требуемой точности преобразования в каждом канале, с помощью блока 3 установки коэффициентов пересчета задаются соответствующие коэффициенты для пересчетных устройств 2.

При каждом цикле измерений блок 11 управления формирует сигнал, возвращающий в исходное состояние пересчетные устройства 2 и триггеры 4 начала отсчета.

Измерительный счетчик 7 начинает считать импульсы генератора б калиброванной частоты.

Триггер 4 начала отсчета фиксирует момент появления первого импульса на выходе элемента ЗАПРЕТ 1 и устанавливается в состояние «1», разрешая прохождение импульсов генератора б калиброванной частоты, сдвинутых по фазе относительно импульсов счета, через генератор 5 одиночных импульсов на соответствующий информационный вход (каждому входу канала соответствует один разряд блока памяти), а также через элемент ИЛИ 8 на вход записи блока 9 памяти.

Таким образом, при появлении импульса в любом канале измерения или в нескольких каналах одновременно, в блок 9 памяти по адресу, соответствующему коду измерительного счетчика, в соответствующий данному каналу разряд записывается признак (логическая «1» или «О») появления импульса в соответствующем канале (каналах).

После поступления п — 1 импульса в пересчетное устройство 2 триггер 4 начала отсчета вновь устанавливается в состояние «О», После поступления и-ro импульса в пересчетное устройство вновь взводится триггер и соответствующий этому моменту признак данного канала вновь записывается в соответствующий разряд блока 9 памяти по адресу, соответствующему коду измерительного счетчика. Блок коэффициента пересчета при этом запрещает прохождение импульсов через элемент ЗАПРЕТ 1 соответствую щего канал а.

B момент окончания счета на пересчетных устройствах 2 во всех каналах на выходе элемента И 10 формируется сигнал окончания измерений, который поступает в блок 11 управления.

При чтении информации из блока 9 памяти определяют коды адресов признаков каналов, соответствующие кодам измерительного счетчика на момент прихода 1-го и п-го импульсов счета.

Вычисление измеренных значений частоты производится по формуле

F„. ng

>it — >ai где ; — результат измерений в i-м канале;

F — калиброванная частота;

n, — коэффициент пересчета в i-м канале;

Л „— код измерительного счетчика (адрес ячейки в блоке памяти) в момент начала отсчет в i-м канале;

Л „— код измерительного счетчика (адрес ячейки в блоке памяти) после заполнения пересчетного устройства в i-м канале.

Формула изобретения

Многоканальный преобразователь частоты в код, каждый из каналов которого содержит логический элемент ЗАПРЕТ, первый вход которого соединен с источником преобразуемого сигнала, а выход и второй вход соединены соответственно с входом и и выходом пересчетного устройства, второй вход которого соединен с блоком установки коэффициента пересчета, триггер, соединенный по входу с выходом элемента

ЗАПРЕТ, а по выходу — с первым входом генератора одиночных импульсов, причем выходы пересчетных устройств всех каналов соединены через многовходовый логический элемент И с блоком управления, выход которого соединен с вторыми входами триггеров, третьими входами пересчетных устройств и первым входом измерительного счетчика, а его второй вход соединен с первым выходом генератора калиброванной частоты, второй выход которого объединяет вторые входы генераторов одиночных импульсов, выходы которых соединены с информационными входами блока памяти, отличающийся тем, что, с целью упрощения преобразователя, в нем выходы генераторов одиночных импульсов через логический элемент ИЛИ подключены

712953

Составитель Л. Багян

Техред А. Камышникова

Корректор Е. Хмелева

Редактор И. Грузова

Заказ 2780/14 Изд. № 113 Тираж 995 Подписное

11ПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

5 к входу записи блока памяти, адресные входы которого соединены с выходами измерительного счетчика, а выход (n — 1) -го разряда каждого пересчетного устройства соединен с входом соответствующего триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство № 296051, кл. G 01R 23/02, 1971.

5 2. Авторское свидетельство № 598237, кл. Н ОЗК 13/24, 1976 (прототип).