Устройство для точечной записи информации

Иллюстрации

Показать всеРеферат

Союз Советских

Соцна<т<нстмческчк

Ресттубпик

ОП ИСАНИЕ .И ЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

71И38

43 (6!1 Дополнительное к лвт. свил-ву-(22! Заявлено 02.09.76 (211 2402944/!8-24 с присоединением заявки №-(28! Приоритет —<й< 06 К !5/14

Гевудлрстеекнь<)(катт<пет

СССР в делам каобретеккк

<т т)ткрмт<<к

Опубликовано 05.г(2.80. Бюллетень № 5

Дата опубликования Описания (5.02.80 (58) УДК 681 327, .1 (088.8) (72) Авторы изобретения

A. M. Муртлзии и И. . 1!Олищук (7P) Заявитель (541 Н .TРОЛСТВО ДЛЯ 0

ИНФОРМАЦИИ

Изобретение относится к области автоматики и вычислительн()й техники, в частности, к устройствам для визуального прелставления информации.

Известно устройство для точечной записи информации, содержащее дешифратор, выполнен(и»й по двухступенчатой схеме, вторая ступень которого выполнена на ферритовых сердечниках с несколькими обмотками, блок печати с элементал<и памяти нл тиристо()ях f (f.

Известно также устройство лля точечной записи информации, содержа(нее блоки памяти, лешифрлт<»р и блок печати, иодключ (<((If(< к лентопротяжному механизму, выхол которого п<»лключсп к ллтчику скорости, трип(р управления, элемент ИЛИ !2Я.

В изн(стиых устройствах информация. поллежащля регистрации, сначала лешифрируется. л затем зап«миилется в первых элементах памяти и но сигналу датчика скор<и ти иереписывлется во втопые элементы памяти, tT() связано с ил»(ичием большого коли цстпл < Вя:и и ме>клу леишфратором и блоком ff< (лти, и слелсвлтельио трудоем2 костью изготовления регистрирующего устройства.

Цель изобретения -- упр(ицеиие устройства.

5 Это лостиГястся тем что ус7 ройстпо (Одержит группы элементов !1, группу элементов И,(!И и формирователь разрядности строки, Вьшолнсниый в ниле п«следовательно соединенных триггера, гсисрлторл н счетчика, полклк)че(щого к нулевому входу триггера, елиничный вход котороп» соединен с выходом датчика скорости и с блоком печати, соелиненным с триггером упрлвления, выхолы счетчика подклю((н(» к« Входам де(иифрлтора и к одним из (

Bx(лу устройства, лруп<е В)н»лы к ВыХо,li ) РИГГЕРЛ УИРЛ(37(3<3<Я, Л В(»ХОЛ(» Э7(M«. <т(»В ! обеих груни соедин< иы <О (»х<»л(<ми эл(л< . и ГОВ И И Г()ytt(tf», В((х«;(3» к<»Г<»р« х полл. ((<) лень(к я

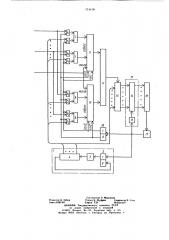

fia е(. ртеже представлена блок-схема устройства.

Уст!)Ой< твО для точечной записи информации содержит формирователь разрядности строки 1, выполненный B виде последовательно соединенных тригп ра 2, генератора 3, счетчика 4, подключенного одним выходом к нулевому входу триггера 2. Дру, гие выходы счетчика 4 и первые входы устройства подключены к одним из входов групп элементов И 5, 6 соответственно.

Выходы элементов И 5, 6 через элементы

ИЛИ 7, 8 соединены с адресными входами блоков памяти 9, 10, к разрядным входам которых полключены вторые входы устройства.

Выходы блоков памяти 9, 10 через элемент ИЛИ l! подключены к первому входу дешифратора 12, к другим входам которого полключены выходы счетчика 4; выходы дешифратора 12 соединены с блоком печати 13, содержащим усилители 14 и формирователь времени печати 15. Блок печати 13 соелинен с лентогеротяжным механизмом 16, к выходу которого подключен датчик скорости 17, соединенный с блоком печати 3, единичным входом триггера 2 и триггером управления 18, полключенным к блокам памяти 9, 10 и другим вхолам групп элементов И 5, 6.

Устройство работает следующим образом, После включения лееетопр(ее(тяже<ого механизма 16 латчик скорости 15 формирует импульс, соответствующий перемещен))<о бумаги на заданную величину, например, па

0,5-;-0,6 мм., По импульсу датчика скорости 5 предварительно обнулешеые триггеры 2, 18 устанавливаются в елнееичееое состояние.

llотенциал с единичного выхода триггера »а вход «запись» блока памяти 1О, на вход «чтение» блока памяти

9 и на первые входы элементов И6а, 5!, разрешает запись вхолной информации в блок памяти 10 и считывание информации из блока памяти 9, Количество ячеек каждого из блоков памяти 9, 10 равно количеству пишущих электродов лентопротяжного механизма 16, )е каждвя ячейка памяти соответствует «своему» пишущему электроду.

При записи информации в блоки памяти адрес ячейки определяется значением входной информации, а в качестве разряда записывается синхроим пульс сопровождения входной информации.

Когда триггер 18 находится в единичном состоянии входная информация через элементы И6, ИЛИ 8 поступает,иа адресные вхолы блока памяти 10, на разрядный вход котороео ееостунает синхроимпульс сопровождения данного значения информации, и произееолнтся ваше h информации в блок памяти !0; причем, если некоторые зна )ения вход)(ой ипформаеьии будут повторяться несколько раз, то согт<>яние соогпетствук>щих ячеек блока памяти !0 будет полтвержлаться.

С)лееовремееееео с записью информации в блок памяти l 0 производится с IHTb!RBHHP. нулевой информации из блока памяти 9, так как блоки памяти перел началом регистрации Обнуляют. (6

Формирование адреса блока памяги при считывании информации происхолит слелующим образом.

Разрешаеощим сппгалом триггера 2 запускается генератор 3, импульсы котороЯ$ го постъпезl()t в и-разрядив! н счетчик 4, Гл( п -- количество разрядов входной информации.

КОЛЫ разрядов счетчика 4 через элементы И5), ИЛИ 7 поступают на адресные

29 шины блока памяти 9 и одновременно поступают ееа вторые вхолы лсш)ефратора 12.

Выходы дешифратора (количество которых

Определяется как N = 2") через усилитель

14 соединены с соответствую)ними пишущими электродами лентопротяжног(> механизм ма 16. (!астота повторения импульсов генератора 3 обеспечивает считывание из всех ячеек блока памяти 9 за время протягивания бумаги на 0,5-:-0,6 мм.

Импульсом переноса счетчика 4 триггер

36

2 обнуляется, генератор 3 прекращает работу ло прихода слелующего импульса датчика )7, счетчик 4 тоже устанавливается в пулевое состояние. .По следующему второму импульсу латslI чика скорости 17 триггер !8 перебрасывается и нулевым выходом переклеочает блок памяти 9 на «запись», а блок памяти 10 на «чтение»; Одновременно разрешающий сеегееал появляется на первых входах элементов И 6!, 5)) элементы И 6), 5! заире()(а к)тся.

Входная информация поступает через элементы И6<, ИЛИ f на адресные входы блока памяти 9, на разрядный входрблока памяти 9 поступают синхроимпульсы сопро4» вождения входной информации, признак наличия информации, и идет запись в блок памяти 9.

По второму же импульсу датчика скорости 17 триггер 2 снова устанавливается в единичное состояние; запускается генератор 3 и счетчик 4. Первый импульс генератора на выхоле счетчика формирует код

00...01 — соответствующий адресу 1-Ой ячейки блока памяти 1О и считывается содержание первой ячейки.

$3 Если в предыдущем, первом такте в l-yx) ячейку блока памяти 10 был заееисан признак наличия информации, то из Т<>Н ячей. ки считывается единица и на выхО ц. элемен

71 !! та И,. 111 1! формируется импульс, стр >би руниций д< шифра гор 12, иа вход которог<> поступает код 0...01 «.t счетчика 4.

1< гдл нл первом выходе дешифрлторл !2 появляет< я импульс. возбуждакпций через с«ответствунцций у< илитель 14 ток записи иа игрв«ч шппуьцем электроде. Длительность импульса тока записи определяется типом используемой бумаги и задается формировзтглгч времени печати 15 по импульсу

JQffT ffff<3 скор« T

11осле считынлиия из всех ячеек блока <г> памяти 10 с дешифрзцией тех значений счетчика 4. по которым из блока памяти 10 считывался признак наличия информации, импульсом переноса счетчика 4 триггер 2 обнуляется.

1$

Каждое значение информации — — признак наличия информации — считывается из бл<>ка памяти только один раз, поэтому на участке 0,5 мч Г>учаги прописывается только одна точка. Тлк обеспечивается про- 2î реживание неизх<еняю (ейся информации. .11ри этом ни одно измсияницееся значение информации не теряется, так как каждому значеникэ информации соответствует «своя» ячейка памяти.

В предлагаемом устройстве дешифратор

I2 расположен после блоков памяти, выполиенных иа больших интегральных схемах, з считывание информации из ячеек памяти производится последовательно. Это позволяет сократить связи между блоками и элечеитачи устройства, упрогцлет его конструкцик> и снижает трудоемкость изготовлеш<я.

Введение формирователя разрядносги строки позволяет прореживать неизмеияюгцуюся информацию, что исключает возможНОСТЬ раэруШЕИИя <>С<<«ВЫ 6уЧЛ<И И ум И<, шлгт износ И1<ц>ущих электр«д«и.

Формили (<л(>бр(>е><ич

Устро<<ство для точе tfl(>f1 записи НИ<1>«р. мании, содгржашге блоки плмп>и, д<чииф рлтор и блок печати. Иодклк> и иный к .И>по протяжному мгхаиизчу, вых«д к<>т< р«г(> п<>лклк>чен и датчику скорости, триг>(р упрлвления, элемент ИЛИ, отличакзщс<((f< ч, чг«, с целью упро<цеиия устройствл, ои«г«дгр жит группы элел(еитов И, группу элементов ИЛИ и формирователь разряди«сти < f p«ки, выполиеииый в виде п<>следовлт< льп<> соединенных триггера, гги< рат«рл и счетчика, подклк>ч(íf<îãо к нулевому входу тр<пгерл, единичный вход которого c<><дииги с выходом датчика скорости и с блок«ч пгчлти, соединениым с тригггроч управления, Bbf

ХОДЬ< СЧЕТЧИКа ПОДКЛЮЧЕHM КО ВХ<>ДЛМ Д(. шифратора и к одним из вход«в элгчгнТов И пгрвой групп(><, друп<е входы к<>т«рых подключены к триперу упрлвлгния, гогди пенному с блоком плл<яти, одпи из вх«д«н элементов И второй группы п«дклк>чгньl ко входу устройства, други(входы — - к 1>ь<ходу трипера упрлвлеш(я, л выходы эл< чгитов И обеих групп соединены с«Их«дачи элгчгитов ИЛИ группы, выходы к«т«рых подклк>чены к адресным входлч 6л«к(>в плчяти, входы элемента ИЛИ подклн> и fff < к f

ИстОчники ииформлции, принятые во внимание при >кг(ц 1>.<и;>е

1. Авторское свидетельство (. (.(;! № 491142, кл. (> 06 К 15/22, 03.0Г>,70.

2. Авторское свидгтел(ств<> (:(.(;! № 329545, кл. б 06 К 15/14. 05.0! .70 (rlр« тоти п1.

Составитель А. Муртазии

Редактор Д. Зубов Техрел К. Шуфрич Корректор Н. Сгец

Закал 9292/49 Тираж f51 Подписное

КИ ИИ ПИ Госуларственного комитета СССР по делам изобретений и открнтий

1 I 3035, Москва, )К вЂ” 35, Раушская наб., д, 4/5

Филиал ППП «Патенте, г. Ужгород. ул. Проектная. 4