Устройство для передачи информации

Иллюстрации

Показать всеРеферат

<»714494

Союз Советских

Социалистических

Республик c "

«» (61) Дополнительное к авт. свид-ву (22) Заявлено 25.04.75 {21) 2128831/18-24 (51)м. Кл.

G 11 С 9/02 с присоединением заявки М 2129033/18 — 24

Риударатввннъй квмнтвт

СССР ло делам изобретений к атхритнй (23) П риоритет

Опубликовано 05.02.80. Бюллетень М 5

Дата опубликования описания 05.02.80 (53) УДК 681.327.,66 (088.8} (72) Авторы изобретения

B. M. Сентюрин и А. И. Васильев с

Институт электронных управляющих машин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ

Изобретение относится к вычислительной технике и может быть использовано в устройствах передачи информашги.

Известно устройство для передачи информации, содержащее регистры, сумматор, элементы И, дешифратор, блок управления (11.

Однако это устройство обладает невысоким быстродействием и имеет сложную структуру.

Наиболее близким из известных по технической сущности является устройство, содержаto шее основной и вспомогательный регистры, шесть блоков элементов И, два блока элементов ИЛИ.

Это устройство выполняет элементарные функции сдвига содержимого регистра влево

35 или вправо, а для выполнения более сложных функций сдвига, например, упаковки распакованных чисел и распаковки упакованных чисел необходимо применение соответствующей под,программы что связано с использованием

Э

2О основной памяти ЭВМ объемом около

200 байт Р1.

Однако выполнение подпрограммы представляет собой процесс, последовательно выполняю.

2 шихся команд за большой ш тервал времени, измеряемый в 350 — 500 тактовых импульсов, что не позволяет увеличить скорость упаковки (обработки) распакованных чисел (информации), Цель изобретения — повышение быстродействия устройства.

Это достигается тем, что в устройство для передачи информации, содержащее основной регистр, выходы которого подключены к первым входам первых элементов И и к выходам устройства, выходы первых элементов И через первые элементы ИЛИ соединены с одними из входов вспомогательного регистра, выходы которого подсоединены к одним из входов вторых элементов И, первые выходы вторых элементов И соединены с одним из входов вторых элементов ИЛИ, выходы которых подсоединены к одним из входов основного регистра, блок управления, введены блок формирования кода, блок декодирования, один иэ выходов которого соединен со вторымн входами первых элсментов И. Другие выходы блока декодирования подключены к другим

14494 4 0

3 7 I . входам вторых элементов И, Один иэ входов блока декодирования соединен с выходом ос- новного регистра. Другие входы блока декодирования соединены с одним из входов устройства, другие входы которого подключены ко входам блока формирования кода, выходы которого соединены .с третьими входами первых элементов И, четвертые входы первых элементов И соединены с первыми выходами блока управления, вторые, третьи и четвертые выходы которого соединены с другими входами вспомогательного регистра, с другими входами вторых элементов И и с другими входами основного регистра .соответственно.

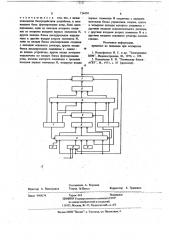

На чертеже представлена укрупненная функциональ1гая схема устройства.

Устройство содержит основной регистр 1, вспомогательный регистр 2, элементы И 3 и 4, элементы ИЛИ 5 и 6, блок управления 7, блок формирования кода 8, блок декодирования 9.

Устройство работает rr режимах упаковки и распаковки.

В режиме упзковки в исходном положении распакованное число находится в основном регистре 1, знак числа — в старшем (правом) байте, а в остальных байтах находится число, в котором цифры расположены по убыванию . старшинства справа налево. Если число состоит из (N 1) цифры, то оно упаковывается эа 1 такт, и результат заносится в младшую " половину основного регистра 1, причем знак помещается s младшую тетраду: последнего байта, а цифры в остальные тетрзды — младшими разрядами в сторону знаковой тетрады à операция производится в 2 полутакта, В первом полутакте содержимое всех байтов основного регистра 1, кроме старшего, через элементы 3 переводится во вспомогательный регистр 2, а в старший байт этого регистра заносится ноль из блока 8. Во втором полутакте через открытые элементы И 4, элементы

ИЛИ 6 в младшую тетраду основного регистра

1 вводится информация с блока 9 (зона знака), а в остальные тетрад младшей части основного регистра 1 переводится содержимое младших тетрзд всех байтов кроме старшего вспомогательного регистра 2. Если число состоит менее чем из (N —;"то нз вто-. ром полутакте первого такта элементы И 4 закрыты, а часть элементов И 4 открыта. Производится обычный сдвиг информации основного регистра 1 на один байт "rrrrparro, йри этом старший знаковый байт в сдвиге не участвует, а в освободившиеся левые байты, кроме старшего, заносятся нули с блока фор мирования кода 8; Блок управления 7 формирует столько тактов сдвига, на сколько коли)

40 чество цифр в чйсле меньше (й — I). После завершения всех тактов сдвига часть элементов 4 закрывается, часть элементов 4 открывается и происходит занесение результата упаковки в основной регистр, как это было описзно выше для случая когда число цифр равно (М 1).

В режиме распаковки, как и при упаковке, исходное число загружается в основной регистр

1, в его младшую половину со знаком в самой младшей тетраде. После запуска устройства первым тактом содержимое scex тетрзд младшей части основного регистра 1, кроме самой млздшей (знаковой) тетради, блоком управления 7 через часть элементов И 4 переводится в младшие тетрзды всех байтов, кроме старшего, вспомогательного регистра 2, а содержимое младшей тетрады, преобразованное блоком декодирования 9 (зона знака), вводится в старший байт регистра 2. На том же такте с блока формирования 8 кода в старшие тетрады всех байтов, кроме старшего вспомогательного регистра 2, вводится код зоны, Затем содержимое регистра 2 переводится через часть элементов 4 и элементы ИЛИ б в основной регистр 1. Если число содержит (1ч — 1) цифру, на этом операция заканчивается, а в основном регистре находится распакованное число. Если число состоит из (N-1 — к) цифр, начинается операция сдвига информации основного регистра на 1 байт влево, состоящая из К циклов, после чего в основном регистре оказывается требуемое распакованное число. Старший байт основного регистра 1 в операции сдвига не участвует.

Введение дополнительных блоков и соответствующих связей между ними позволяет сократить интервал времени распаковки упако-. ванных чисел с 300 — 500 машинных тактов до

1 — 8 машинных тактов, уменьшить необходимый обьем памяти в ЭВМ на 200 байтов, упростить программирование.

Формула изобретения

Устройство для передачи информации, содержащее основной регистр, выходы которого подключены к первым входам первых элементов И и к выходам устройства, выходы первых элементов И через первые элементы ИЛИ соединены с одними из входов вспомогательного регистра, выходы которого подсоединены к олним из входов вторых элементов И, первые выходы вторых элементов И соединены с одним из входов вторых элементов ИЛИ, выходы которых подсоединены к одним из входов основного регистра, блок управления, 714494

Составитель A Воронин

Техред М.Петко

Корректор A. Гриценко

Редактор А Виноградов

Заказ 9908/74

Тираж 662 . Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП ™Патент", r. Ужгород, ул. Проектная, 4 о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены блок формирования кода, блок декодирования, один из выходов которого соединен со вторыми входами первых элементов И, другие выходы блока декодирования подключены к другим входам вторых элементов И, один из входов блока декодирования соединен с выходом основного регистра, другие входы блока декодирования соединены с одним из входов устройства, другие входы которого подключены ко входам блока формирования кода, выходы которого соединены с третьими входами первых элементов И, четвертые входы

:первых элементов И соединены с первыми выходами блока управления, вторые, третьи и четвертые выходы которого соединены с другими входами вспомогательного регистра, 5 с другими входами вторых элементов И и с другими входами основного регистра соответственно.

Источники информации принятые во внимацие при экспертизе!

1- Ксенофонтов И. С. и др. "Электронные

ЦВМ", Машиностроение, М., 1970, с. 109..2. Пилипчатин E. Н. "Логические блоки .

АСВТ", М., 1971, с. 87 (прототип).!