Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

© П И А Н И Е < 714504

ИЗОБРЕТЕН ИЯ.Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22)Заявлено 23.09.77 (21) 2530312/18 24 (5() М. Кд. с присоединением заявки Ж

О 11 С 29/00. Веуаеретеекаьй кемитет

CCCP. в делам нзабретеккй н еткрытиЯ (23) П риоритет (5З) Уд (68 1.327. . 17 (088.8) Опубликовано 05.02.80, Бюллетень ¹ 5

Дата онубликоваиия описания 10 02,8 (72) Авторы В. П. Андреев, A Н. Пресняков, A. H. Ивано изобретения В, Ф. Семенов, A. В. Мысов и Ю. A. Карелин

Особое конструкторское бюро вычислительной техники

Риз анскоть радиотехнического института (71) Заявитель (54) УСТРОЙСТВО ДДЯ КОНТРОЛЯ ПАМЯТИ

Изобретение относится к области за- поминающих устройств.

Известно устройство для контролй памяти, содержащее блок формирования команд, формирователи управляющих то- ков, блок сравнения . 1).

Недостатком этого устройства является малое быстродействие.

Известно также наиболее близкое к тО данному изобретению устройство для контроля памяти, содержащее блок формирования команд и эталонов и блок сравнения, входы и выходы которых подключены к выходам и входам устройства j2).

Частота работы этого устройства мент -. ше предельно возможной частоты работы блока памяти. B нем формирование следующего обращения происходит лишь после анализа считываемой из, контролируемого блока памяти информации. B связи с этим невозможно проверить ряд полупроводниковых блоков памяти, допус2 каюших режим работы с перекрывающимися во времени обращениями. Это сужает область применения устройства.

Целью настоящего изобретения является расширение области применения устройства за счет обеспечения возможности контроля блоков памяти, допускающих параллельную обработку обращений.

Поставленная пель достигается тем, что устройство содержит буферный накопитель эталонов, входы которого подклкг. чены к выходу блока формирования команд и эталонов и одному из входов устройства, а выходы соединены с одними из входов блока сравнения.

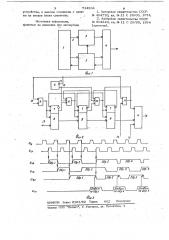

На фиг; 1 изображена блок- =хема устройства; на фиг. 2 представлен один из возможных вариантов буферного накопителя эталонов; на фиг. 3 показана вре« менная диаграмма работы буферного накопителя эталонов.

Устройство содержит блок 1 формирования команд и эталонов, выход 2 которого подключен к входам буферного накоI Таким образом, за счет обеспечения возможности контроля блоков памяти, допускающих паралл пьную обработку об40 ращений, существенно расширяется область применения устройства.

3 71450 пителя 3, и блок 4 сравнения. Один из входов накопителя 3 подключен к входу устройства. К входам и выходам устройства подключается контролируемый блок

5 памяти.Буферный накопитель 3 эталонов содержит генератор 6, триггеры занятости 7 регистров 8, двухвходовой элемент

И 9, трехвходовые элементы И 10, двухвходовой элемент 11. Шина 19 запаса эталона и кодовые шины 13 эталона соединяют буферный накопитель 3 эталонов с блоком 1, шина 14 сопровож дения соединяет блок 3 с контролируемйм блоком 5, а в блок 4 сравнения информация, считанная на блок 5, поступает по кодовым шинам 15.

На фиг. 3 изображены сигналы И.„< и

И на прямом 16 и инверсном 17 выхоl дах генератора 6, сигналы И - И > ка выходах 18-20 первого, второго и третье

I го регистров 8 и сигнал И состояния шины 14 сопровождения, соответствующий появлению информации, считанной из, блока 5 памяти (ответ по первому обра 25 щению — обр. 1, ответ по второму обращению - обр. 2 и т д}. Устройство работает следу|ощим образом. зо

Блок 1 формирует команды, поступаю" щие в блок 5, и при командах считывания формирует эталоны, которые поступают на входы накопителя 3. Задержка в формйровании команд и эталонов происходит з лишь на время, когда контролируемый блок 5 занят.

В буферном накопителе 3 эталонов (на фиг. 2 показано только три регистра 8) с каждым тактом генератора 6 про "исходит продвижение эталонов на очередной незанятый регистр 8, то "есть соз дается некоторая очередь эталонов. г-—

В первый регистр 8 эталон записывается по фронту импульса с инверсного выхода 17 генератора 6 при наличии управляющего сигнала на шине 12 запи-i си эталона. Во время действия импульса с прямого выхода 16 генератора 6 sa анализируется наличие эталона в данном регистре 8, состояние следующего регистра и если в данном регнстре есть информация (триггер 7 в единичном" состоянии),а следующий регистр свобо- ы ден (триггер 7 этого регистра в нулевом состоянии), то по спаду импульса йроисходит" перемещение эталона из дан-

4 4 ного регистра 8 в следующий, обнуляется триггер 7 данного регистра, и переводится в "единичное состояние триггер

7 следующего.

Из последнего регистра информация выдается в блок 4 сравнения при наличии считанной из блока 5 информации.

Триггер 7 последнего регистра обнуляется после выдачи эталона в блок 4 сравнения., Та (им образом каждому ответу контролируемого блока 5 соответствует эталон, поступающий из накопителя 3.

Нормальная работа устройства возможHB толькО пОсле соответств чОщих нач аль ных установок, в частности, перед началом контроля все триггеры 7 должны быть обнулены. Ыепи начальных установок не показаны. Блок. 4 сравнения сравнивает поступившую из блока 5 информацию и эталоны и выдает результаты на выход этого блока. Если необходима длительнач выдача информации о сбое, например при ручном способе регистрации, то блок 4 сравнения может содержать триггер занятости и выдавать информацию о своем состоянии и блок 5. Количество регистров 8 в накопителе 3 должно соответствовать максимально возможному количеству обращений за считыванием информации, параллельная обрабо1 ка которых возможна в контролируемом блоке 5. г

Формула изобретения

Устройство для контроля памяти, содержащее блок формирования команд и эталонов и блок сравнения, входы и вы ходы которых подключены к выходам и входам устройства, о т л и ч а ю ш е е с я тем, что, с целью расширения Области применения устройства за счет обеспечения возможности контро)и блоков памяти, допускающих параллельную Обработку обращений, око содержит буферный накопитель эталонов, входы которого подключены к выходу блока формирования команд и эталонов и одному из входов

5 714504 устройства, а выходы соединены с одними из входов блока сравнения,; №

Фиг. 7

4hg. ß

ЦНИИПИ Заказ 9301/52 Тираж 662 Подписное

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4

Источники информации, принятые во внимание при экспертизе. ю

l. Авторское свидетельство СССР

494770, кл, & 11 С 29/00, 1974.

2. Авторское свидетельство СССР

¹ 504249, кл. G 11 С 29/00, 1974 (прототип).