Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

(ii 716О63

Союз Советскик

Социалистически«

Республик

Г:. 1т т,.5" (2,, с (Я)м. Кл. (61) Дополнительное к авт. свид-sy (22) Заявлено 10.07,78 (21) 2640143/18-24

G 11 С 9/00 с присоединением заявки J4(23) Приоритет

Государственнв|й коинтет

СССР оо делам нэооретеннй н от«ритой (53) УДК 681.327. . 6 (088.8) Опубликовано 15.02.80. Бюллетень 1че 6

Дата опубликования описания 18.02.80

В. В. Ткаченко и М. А. Летов (72) Авторы изобретения (71) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и предназначено для накопления инфор

:мационных сигналов в порядке их по ступления.

Известно устройство, содержащее группы последовательно соединенных запоми-

5 нающих ячеек и соответствующие каждой такой группе управляющие ячейки (11.

Однако в этом устройстве необходимо использование для накопления последова»

0 тельно поступающей на вход информации двух запоминающих ячеек для накопления соответственно нулевой и единичной информации. Кроме этого, последовательное прохождение информационного сигнала через группы запоминающих ячеек в соответствующую запоминающую ячейку, а также необходимость стробирования момента подключения на запись следующей запоминающей ячейки, после записи в предьтдущую запоминающую ячейку, снижают быстродействи е устройства.

Известно также устройство с тремя внешними входами, содержащее четыре

2 трехвходовых элемента И HE для положительных сигналов, два из которых образуют трщтер с раздельными входами, а два других подключены ко входам триггера, выходы которого подключены к попарно соединенным входам двух других элементов И-HE (2).

В таком устройстве отсутствует фиксация момента окончания накопления информации, что не позволяет без дополнительного устройства управления использовать такие ячейки для накопления информа» ционных сигналов в порядке их поступле- ния., Наиболее близким техническим решением к изобретению является буферное запоминающее устройство, содержащее группу последовательно соединенных каскадов, в каждый из которых входит запоминающая

У и управляющая ячейки (3j.

Недостатками такого устройства являются низкое быстродействие вследствие рередачи информации в соответствующую запоминающую ячейку через предшествую3 71606 щие такие ячейки, сложность управляющей ячейки, в которэй необходим подбор элементов для достижения максимально возможного для этого устройства быстродействия, а также низкая надежность из-за возможной потери информации при перено се ее в соответствующую запоминающую ячейку вследствие независимой работы запоминающих и управляющих ячеек.

Мелью. изобретения является повышения 1о быстродействия и надежности устройства.

Это достигается тем, что каждая управ ляющая ячейка выполнена на элементах

И-ИЛИ, первый и второй входы первой группы входов элементов И-ИЛИ соедине- )5 ны с выходами первого и второго элемен-: тов И-HE каждой запоминающей ячейки, третьи входы первой группы входов элементов И-ИЛИ. соединены с управляющей шиной, а выходьг элементов И-ИЛИ, кро- 20 в(э.первых, соединены с первым входом второй группы входов элементов И-ИЛИ, l с третьими входами третьего и четвертого; элементов И-НЕ и со вторым входом втррой; группы входов предыдущих элемен- 25 тов" И ИЛИ, второй вход второй rpyrrm входов последних элементов И-ИЛИ является-входом установки устройства в исходное состояние, а выход первых элеменгов

И-ИЛИ соединен с первым входом второй ЗО группы входов данного элемента и с управляющей шиной.

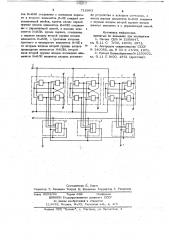

3 Д перепада на схеме И-HE связанной с другой информационной шиной, по которой в данный момент информация не поступает, соответствует окончанию работы запоминающей ячейки. Этот перепад посгупает на первую группу входов элемента И-ИЛИ, куда поступает и входной сигнал, Таким образом, управляющаи ячейка сработает только после окончания входного сигнала, » при этом на выходе ее установится уровень «1, который разрешает запись следующего информационного сигнала, поступающего в устройство, в запоминающую ячейку предыдущего каскада.

Запись в остальные ячейки проводится аналогично. Уровень "1" на выходе управ- . ляющей ячейки первого каскада указывает на окончание записи информации во все устройство. По окончании обработки информации, поступившей в устройство, по шине подготовки устройства к приему подается отрицательный импульс, и устройство устанавливается в исходное состояние.

Предлагаемое буферное запоминающее

l устройство благодаря использованию в ка честве управляющей ячейки элементов И-

ИЛИ, соединенных с соответствующими запоминающими ячейками и входной управш ющей шиной, обладает более высоким быстродействием и надежностью по сравнению с известным, G также некритично K разбросу параметров входящих. в него элементов, т.е. не требует их подбора.

На чертеже дана структурная схема буферного запоминающего устройства. 35

Оно содержит запоминающие ячейки-. 1, соединенные с входными Я и Я и вы. ходными шинами, а также с соответствую шими управляющими ячейками 2, соединенными со входной управляющей шиной Я-Я, к»-оторай служит- для подачи сигнала о наличии информации на входе устройства.

Устройство работает следующим образом.

В исходном состоянии на входных ши« 45 нах, а также на выходах запоминающих ячеек 1 установлен уровень 1"; на первых и вторых входах первых групп входов, а также на выходах управляющих ячеек 2 установлен уровень О, $0

При подаче сигнала по одной из входных информационных шин .5 или R a таКже сигнала я — Q, по входной управлякщей шйне информаций записывается" B последнюю запоминающую ячейку. При этом 55 на выходах трехвходовых схем И-НЕ этой запоминающей ячейки появляется йоложительный перепад, причем появление такого

Формула изобретен 8s

Буферное запоминающее устройство, со держащее управляющие и запоминающие ячейки, причем каждая запоминающая ячейка выполнена Ва четырех трехвходовых элементах И-НЕ, первые входы первых и вторых элементов И-НЕ подключены к со-, ответствующим входным информационным шинам, первый вход третьего элемента

И-HE подключен ко вторым входам первого, второго и выходу четвертого элемен тов И-НЕ, первый вход четвертого элемен» та И-НЕ подключен ко второму входу третьеГо И .третьим входам первою и второго элементов И-НЕ, а выход второго элемента И-НЕ соединен со входом четвертого элемента И-НЕ, о т л и ч а ющ е е сятем,,что,,с целью повышений надежности и быстродействия устройства, каждая управляющая ячейка выполнена на элементах И«ИЛИ, при этом первый и вто рой входы первой группы входов элемен716063

Составитель Е. Клиот

Редактор T. Клюкина Техред H. Ковалева Корректор Г. Решетннк

Заказ 9534/44 Тираж 662 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., a. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 тов И-ИЛИ соединены с выходами первого и второго элементов И-НЕ каждый зат поминающей ячейки, третьи входы первой группы входов алементов И-ИЛИ соединены с управляк цей шиной, а выходы эле- 5 ментов И-ИЛИ, кроме первых, соединены с первым входом второй группы входов. элементов И-ИЛИ, с третьими входами третьего и четвертого элементов И-HE u со вторым входом второй группы входов предыдущих алементов И-ИЛИ, второй вход-второй группы входов последних элементов И-ИЛИ является входом установки устройства в исходное состояние, а выход первых элементов И-ИЛИ соединен с первым входом второй групп7 7 входов данного элемента и с управляющей шиной.

Источники информации, принятые во внимание при экспертизе

1. Патент CIIIA М 2588847, кл. G 11 С 7/00, 19/00, 1971.

2. Авторское свидетельство СССР

М 340085, кл. Н 03 К 17/26, 1971.

3. Патент Великобритании J% 1293032, кл. G 11 С 9/00, 1972 (прототип).