Устройство для вычисления суммы произведений

Иллюстрации

Показать всеРеферат

1Ц717765

Союз Советсиик

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (51)М. Кл.

G 06 Г 7/50

I (6l) Дополнительное к авт. свнд-ву (22) Заявлено 04.07.73 (21) 1939962/18 24 с присоединением заявки Ю (23) П риоритет

Опубликовано 25.02,80. Беллетень М 7

Ввудврствевай квинтет

СИР ю аввзм вмбретвввв а вткрмтвв (53) УДК 681.325 (088.8) Дата опубликования описания 28.02.80 (72) Авторы изобретения

Н. П. Вашкевич, Н. Н. Коннов и A. В. Кучин

Пензенский политехнический институт (71) Заявитель

1 (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММЫ

ПРОИЗВЕДЕНИЙ. I

Изобретение относится к области ав° томатики и вычислительюй техники и может быть использовано в цифровых корреляторах и цифровых фильтрах.

Известно устройство для умюження

3 чисел непосредственно в дополнительном коде, причем умножение производится так же, как в ппямом (получение псевдопроизведения на накапливакицем сумматоре), с последующей корреляцией псевдопроиэведения (сложение псевдопроизведения с дополнением отрицательюго сомюжите - ля) (Ц .

Однако это устройство сложно.

Наиболее близким по технической сущ, ности к предложенному является устройство для вычисления суммы произведений, содержащее г -разрядный регистр мюжимого, т -разрядный регистр множителя, узел сдвига, зел анализа, узел управления, сумматоры, регистр, элементы И, ИЛИ, группы элементов И, группу элементов ИЛИ, узел анализа переноса, счет-,. чик, прячем прямые выходы регистра мно2 жимого соединены с первой группой входов узла сдвига, соответствующие выходы которого соединены со входами первого сумматора и первыми входами первого и второго элементов ИЛИ. Инверсные выходы регистра множимого подключены к первому входу узла управления. Выход знакового разряда регистра множимого соединен с первым входом узла анализа. Прямые выходы регистра множителя подключены ко второй группе входов узла сдвига. Инверсные выходы регистра мю» жителя соединены со вторым входом узла управления. Выход знакового разряда регистра множителя подключен ко второму входу узла анализа, первый выход которого соединен с первым входом перво-. го элемента И, а второй выход узла анализа подключен к первому входу второго элемента И. Вторые входы первого и второго элементов И соединены с первой шиной управления, а нх третьи входы — с выходом узла управления. Выходы первого и второго элементов И подключены ко

5 ф

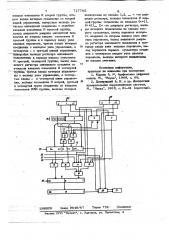

Устройство содержит о -разрядный ре

rHcTp мйОжимого 1, A -разрядный perHCTp множителя 2, узел сдвига 3, представляющий собой комбинационную схему и осу ществляющий смещение кода множимого на один разряд в каждом такте. Выходы знаковых разрядов регистров 1 и 2 под- ключены ко входам узла анализа 4, выдающего уровень логической единицы на выходе 5, если сомножители разного зна-ка, и на выходе 6 - если оба сомножите-. ля отрицательные, узел управления 7, на выходе которого вырабатывается запре-щающий уровень логического нуля, если хотя бы один из сомножителей равен нулю, элементы И 8 и 9, элементы ИЛИ

10 и 11, сумматор 12, группу элементов И 13, элемейт И 14, регистр 15, элемент ИЛИ 16, элементы И. 17 и 18, сумматор 19, узел анализе переносов

2О, счетчик 21, входные шины 22-29.

Устройство работает следующим образом»

В каждом i -ом цикле работы очередные сомножители находятся на регистре

1 и 2. По сигналу по шине 28 содержи-. мое сумматора 12 через группу элементов И 13, элемент И 14 и элемент ИЛИ

3.6 заносится на регистр 15; и в сумматоре 19 осуществляется сложение ранее чакопленной суммы с псевдойроизведением вычисленным в предыдущем цикле работы. При этом перенос в сумматоре

19 распространяется на 2 и разрядов.

Сигналом по шине 25 сбрасывается сумматор 12 . По сигналу иа первой иэ шин

24 с выходов узла сдвига,3 в h младших разрядов сумматора 12 поступает множимое, если младший разряд множителя равен 1 и нули, если он равен О. По этому же сигналу с выхода 5 узла ана- диэа 4 через элемент И 8 и элемент

ИЛИ 1О заносится единица в и -ый раз ряд сумматора 12, если сомножители разного знака, или заносится единица в (O-1) разряд с выхода 6 - при отрицательных сомножителях. Тем самым выйолняется часть коррекции псевдопроиэведения. Занесение единицы в и -ый или (и-1)-ый разряд запрещается уровнем логического нуля с выхода узла управления 7, если хотя бы одын из сомножителей равен O. По сигналу на второй

as шин 24 миожимое со сдвигом на один разряд вправо поступает на входы сумматора 12, если (h -1}-ый разряд множитепя равен 1 и т.д. При каждом очередном -сМЫ ж сдвину ого множимого

3 " - 71776 вторым входам первого и второго элементов ИЛИ соответственно, выходы первого и второго элементов ИЛИ соединены со входами и -го и (h-1)-го разрядов первого сумматора 121 .

Однако это устройство имеет низкое быстродействие, так как в нем произво-, дится предварительно перевод в прямой . I код," затем выполняется умножение, а для дальнейшей обработки - обратный перевод. !О

Мель изобретения — повышенйе быстродействия. . Это достигается тем, что в устройстве, выходы 2в, (2n -1),...(o +1)-ro разря- 15 дов первого сумматора соединены с первы- ми входами элементов И первой группы, вторые входы которых по»дключены ко вто рой шине управления. Выходы,n,(й -1)...

1-го разрядов сумматора подключены к N первым входам элементов И второй груп: пы, вторые входы которых соединены со" второй шиной управления, Инверсные выходы регистра множителя соединейы с первыми входами элементов И третьей группы. Выход знакового разряда" множи"теля подключен ко вторь1м входам элементов И третьей группы . и к первому вхо ду узла анализа переносов, третьи входы которых соединены с выходом узла упра»в»ленйя, "а четвертые - с третьей шиной управления. Инверсные выходы реглстра множимого подключены к первым входам элементов И четвертой группы. Выход

" " - зйакового регистра множимого соединен со вторыми входами элементов И четвертой группы, третьи входу которых под ключены к выходу узла управления, а чет; вертые входы - к четвертой шине"управ- ленни. Выходы элементов И второй, тре-

46 тьей и четвертой групп соединейы со вхо-; дами элементов HJIH круппы, выходы которых подключены ко входам 1,2,... n-re разрядов регистра. Выходы элементов И первой группы соединены со входами 45 (и+1), (+2)...., 2 й-го разрядов регист-; ра, выходы которого подключены ко вхо-: дам второго сумматора, выход переюса

kompo б - соедине»н со вторым - вх»одом" уйла анализа переносов. Вьицод знакового

" рЫрй в регйстра-"мйс6кимого подклвчен к третьему" входу узла анализа переносов»

Выхьд»" переносов первого сумматора сое динен с четвертым входом узла анализа переносов, выходы котс рого подключены xo) 55 входам счетчика.

Ф нкциональная схема устройства приведена на чертеже.

717765

ФО

2О

5 с содержанием сумматора 12 перенос распространяется не более чем нап раз"рядов, что и определяет длительность такта получения псевдопроизведения. До момента окончания второго такта получе- нии псевдопроизведения на сумматоре 12 заканчивается распространение переюса в сумматоре 19, первым сигналом по

1 шине 29 сбрасывается регистр 15, и по сигналу иа шине 26 в и старших разрядов регистра 15 через элементы И 18 и элемент ИЛИ 16 заносится инверсный код множителя, если мюжитель отрица-тельный и ни один иэ сомножителей не равен нулю, т.е. на сумматоре 15 выполняется первая коррекция псевдопроизведения, формируемого на сумматоре 12.

Вторым сигналом по шине 29 сбрасывается s нуль регистр 15, а сигналом по шине 27 в его о старших разрядов за. носится код с инверсных выходов регистра 1, если множимое отрипателью и ни один из сомюжителей не равен нулю, т.е» осуществляется вторая коррекции псевдопроизведения, формируемого на сумматоре 12. При выполнении корречци5 перенос в сумматоре 19 расщостраняется ие более чем Ba A разрядов, w.e» такт коррек-. ции ио времени равен такту получении псевдопроизведения, что и позволяет совместить выполнение этих операций. Йо окончании второй коррекции регистр 15 сбрасывается третьим сигналом по шине

29. К моменту окончания сигнала иа ео следней шине 24 на сумматоре 12 сфор мйруется псевдопроиэведение, коррекция которого была выполнена на сумматоре:

19. По сигналу на шике 28 содержимое сумматора 12 записывается на регистр

15, и в сумматоре 19 начинается сложе ние псевдопроизведенря сомножителей с ранее накопленной суммой. Сумматор 12 сбрасывается, цикл работы повторяется сначала для очередных (1+1)-ых сомножителей, В каждом цикле работы переюсы из старших разрядов сумматоров 12 и 19 поступают в схему анализа переюсов 20. В течение цикла могут поступать О, 1 или 2 переноса. Схема передачи переюса управляется знаковыми pasрядами регистров 1 и 2 и вырабатывает сигналы сложений или вычитания в счет- чик 21. В результате выполнения гй циклов работы нв сумматоре 19 и счетчике

21 сформируются в дополнительюм коде значения суммы произведений, знак которой определяется старшим разрядом счег чика усреднения.

Таким образом при получении суммй произведений чисел, представленных в дополнительном коде быстродействие устройства, которое задает допустимую частоту подачи сомюжителей, определяется лищь временем формирования псевдопроизведения операции коррекции псевдопроизведения и суммирование произведений не отражаются на обшем быстродействии устройства.

Формула изобретения

Устройство для вычисления суммы про изведешгй, содержащее tl -разрядный, рэ" гистр мюжимого, и -разрядный рагистр множителя, узел сдвига, узел вналйза, узел управления, сумматоры, регистр, элементы И, ИЛИ, группы элементов И,: группу элементов ИЛИ, узел аылиза пе- реноса, счетчик, причем прямые выходы регистра мюжимого соединения с первой групной входов узла сдвига, соответствующие выходы которого соединены со входами первого сумматора и первыми sxa.дами первого и второго элементов ИЛИ, инверсные выходы регистра множимого подключены к первому входу узла управ лений, выход знакового разряда рег истра множимого соединен с первыми входом узла анализа, прямые выходы регистра мыожителя подключены ко второй группе входов узла сдвига, инверсные выходы регистра множителя соединены со вторым входом уэлв управления, выход знакового разряда регистра мюжителя подключен «о второму входу узла анализа, первый вы ход которого соединен с первым входом первого элемента И, в второй выход узла анализа подключен к первому входу второго элемента И, вторые входы первого . и второго элементов И соединены с первой шиной управления, а их третьи входы - с выходом узла управления, выходы первого и второго элементов И подключены ко вторым входам первого и второго элементов ИЛИ соответственно, выходы первого и второго элементов ИЛИ соединены со входами и -го и (и-1)-го разрядов первого сумматора, о т л и ч в ю: m е е с я тем, что, с целью повышения

: быстродействия, в нем выходы 2rl,(2n1),... (n +1)-го разрядов первого cyM- матора соединены с первыми входами элементов И первой группы, вторые входы которых подключены ко второй шине управления, выходы и, (о -1) ...1-го раз-, рядов сумматора подключены к первым

7, 71 входам элементов И второй группы, вто рые входы которых соединены со второй шиной управления, инверсные выходы ре" гистра множители соединены с первыми входами элементов И третьей груМйы, выход знакового рияда множителя подключен ко вторым входам элементов И третьей группы и к первому входу узла анализа переносов, третьи входь которых соединены с выходом узла управления, а четвертые - с третьей шиной управления, ийверсйь е -выходы регистра множимого подключены к первым входам элементов

И третьей, четвертой группй, выход знакового регистра множимого соединен со вторыми входами элементов И четвертой

" груййы третьи входй котс рак подклмчены к выходу узла управления, а четвертые входы - к четвертой шине управления, выходы элементов И второй, третьей и четвертой групп соединены со "входами элементов ИЛИ группы, выж>ды которых

776 5. 8 подключены ко входам 1,2, ... n -го раз -. рядов регистра, выходы элементов И первой группы соединены со входами (П+1), (и+2)... 2n -го разрядов регистра, выхо ды Которого подключены ко входам второго сумматора, выход переноса которого соединен со вторым входом узла анализа переносов, выход знакового paspsда регистра множимого подключен к тре10 та@му выду уэна анализа переносов, вы ход переносов первого сумматора соединен с четвертым входом узла анализа переносов, выходы которого поаиаочевы ко входам счетчика..

Источники ииформапии, принятые во внимание при экспертизе

1. Карнев A. М. Арифметика цифровых машин. М., "Наука", 1969, с, 68.

2. Домарамий А, И.;и др. Дискретнаи измерительная корреляпйонная система.

М., Наука ., 1965, с. 31-41 (прототип) °

БНИИПИ Заказ 9849/67 Тираж 751 - Подписное

". . .: Ы

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4