Микропрограммный процессор

Иллюстрации

Показать всеРеферат

!

ОП ИСАНИЕ изовритиния

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистических

Республик (ii)717773

Г

1 1 \ (6l ) Дополнительное к авт. свид-ву(22)Заявлено01,12.77 (21)2550316/Х8-24 (51)М. Кд. с присоединением заявки ¹(23) Приоритет

G 06 F 15/00

ВвудэрствениМ кемитет

CCCP

° в явим «зебретений н втеритий

Опубликовано 25.02.80. Бюллетень № 7 !. (53) УДК681.14 (088.8) Дата опубликования описания 28.02.80

В. М. Долкарт, P. P. Пурэ и В. Н. Степанов (72) Авторы изобретения (71) Заявитель (54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР

Изобретение относится к вычислитель. ной технике и, в частности, к проектйро-" ванию микропрограммных процессоров;

Известен микропрограммный процессор, содерж мций операционный блок, постоянную память на схемах большой интегра5 ции, регистр микрокоманд, адресный pkгистр и блок управления и синхронизации

Ь).

Однако такое устройство имеет низкое

10 быстродействие.

Наиболее близким по технической сущности к предложенному является мйкропрограммный процессор, содержащий блок управления, операционный блок, регистр микрокоманд, адресный регистр, постоянную память, дешифратор ветвлений, пер- вый элемент И, причем первый вход пос- тоянной памяти подключен к первому выходу адресного регистра, первый вход которого подключен к выходу первого элемента И, первый вход которого подключен к первому выходу регистра микрокоманд, второй вход первого элемента И соейИИн

2 с первым выходом блока управления, второй выход которого подключен к первому входу регистра микрокоманд, а третий выход блока управления подключен к первому входу операционного блока, второй вход которого подключен ко второму выходу регистра микрокоманд, третий выход которого подключен к первому входу дешифрато ра ветвлений, второй вход которого подключен к выходу операционного блока,при этом выход постоянной памятй подключен ко второму входу регистра микрокоманд

Ю.

Недостатком известною устройства является необходимость параллельного чтения нескольких микрокоманд из постоянно3 памяти для быстрою выполнения условных переходов (ветвлений) по результату выполнения текущей микрокоманды. Это существенно увеличивает затраты оборудования.

Целью настоящего изобретения являетcs упрощение устройства и повышение быстродействия при выполнении ветвлений

717773 4 выхода. Второй выход блока 9 управления стробирует прием мцкрокоманды в регистр

3 микрокоманд. К моменту возникновения сигнала на его первом выходе информация о- .5 в регистре 3 микрокоманд установлена, и этот сигнал открывает первый элемент H

10, который передает содержимое поля 6 адреса в старшие разряды адресного регистра 7.

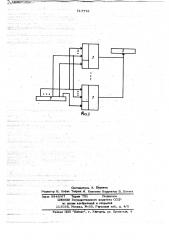

В этот момент операционный блок 1 ен еще не закончил выполнение данной микрокоманды и не выработал условия, необходимые для работы дешифратора 8 ве ге- влений. Однако старшие разряды адресного регистра 7 (фиг. 3) соединены с адло- ресными входами блоков постоянной памялю ти 2, выборка которой начинается после по- установки адресных входов. Входы же выбора блока работают с меньшей задержкой, ок . о чем адресные входы, и могут быть установлены позже. Поэтому младшие разряды адресного регистра 7, выходы которых

Ре- соединены с входами выбора блока посто9 янной памяти 2, устанавливаются через

И второй элемент И 11 импульсом с третье го выхода блока S, управления, который ет формируется после установления переход« нйх процессов в операционном блоке 1. про- Этот импульс осуществляет также передаро-; чу результата выполнения текущей микро30 и команды в регистры операционного блока1. ты- Таким образом, разделение по времени

1, ля установки старших и младших разрядов ад» ресного регистра 7 и управление его младшимц разрядами входами выборе блока постоянной памяти 2 позволяет легко оргале низовать работу без потери быстродейсти-" burrs памяти с ветвлениями по результату ля- выполнения текущей микрокоманды. ей

4О

Время выбора блока в цолупроводниковых постоянных памятях вдвое меньше времени выбора по адресным выходам. ей Микрокоманды с ветвлением по текущему

1 результату составляют 20% от общего та числа мцкрокоманд процессора. Поэтому

45 увеличение быстродействия практически ин составляет 10%.

tro результатам выполнения текущиХ мик роком анд.

Поставленная цель достигается тем, что микропрограммный процессор содержит второй элемент И, первый вход кот рого соединен с третьим выходом блока у управления, второй вход второго элемен та И соединен с выходом дешифратора ветвлений, а выход второго элемента И соединен со вторым входом адресного регистра, второй выход которого соедин со вторым входом постоянной памяти.

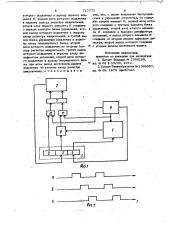

Сущность изобретени я поясняется че тежами, где на фиг. 1 показана блок-сх ма микропрограммного процессора; на фиг. 2 - временная диаграмма работы б ка управления и на фиг. 3 - схема подк ченця щ(ресного регистра к элементам стоянной памяти.

Процессор содержит операционный бл

1, постоянную память 2, регистр 3 мик рокоманд с полем 4 операции, полем 5 ветвлении и полем 6 адреса, адресный гистр 7, дешифратор 8 ветвлений, блок управления, первый и второй элементы

10 ц 11.

Микропрограммный процессор работа следующим образом.

Обработка информации в процессоре, изводится операционным блоком 1. Мик программы хранятся в постоянной памят

2 ца схемах большой интеграции и счи ваются в регистр 3 микрокбмйнд, угфав киций работой операционного блока 1 и формированием. адреса следующей микро команды.

Регцстр 3 микрокоманд содержит но

4 операции, управляющее работой операц онного блока 1, поле 6 адреса, опреде ющее старшие разряды адреса следующ микрокоманды, и поле 5 ветвления, опр деляющее в зависимости от условий ве вления младшие разряды адреса следукщ микрокоманды.

Адрес выбираемой микрокоманды ус навливается в адресном регистре 7, в старшие разряды которого передается формация цз поли 6 адреса, а в младшиес выхода дешифратора 8 ветвлений, кото$O рый формирует младшие разряды адреса в зависимости от кода ветвлений, расположенного в поле 5 ветвления, и условий ветвлений, получаемых as операционного блока 1.

Блок 9 управления синхронизирует ра боту всех блоков процессора. Состояние его выходов во времени показано на фиг. 2: а - первого, б - второго и в - третьего

Формула изобретения

Микропрограммный процессор, содержащий блок управления, операционный блок, регистр мцкрокоманд, адресный регистр, постоянную память, дешифратор ветвлений, первый элемент И, причем первый вход постоянной памяти подключен к первому выходу адресного регистра, первый вход

5 717773 которого подключен к выходу первого эле- тем, что, с целью повышения быстродеймента И, первый вход которого подключен стеня и упрощения устройства, он содер к первому выходу регистра микрокоманд, жнт второй элемент И, первый вход котовторой вход первого элемента И соединен рого соединен с третьим выходом блока с первым выходом блока управления, вто- з -упрюлення, второй вход второго элемен рой выход которого подключен к первому та И соедннен с выходом дешифратора входу регистра микрокоманд, а третий вы- ветвлений, а выход второго элемента И ход блока управлення подключен к перво» соединен со вторым входом адресного ре- му входу операционного блока, второй гистра, второй выход которого соедннен вход которого подключен ко второму вы >о с вторым входом постоянной памят». ходу регистра мнкрокомаид, третий выход которого подключен к первому входу де- Источники информации, шифратора ветвлений, второй вход которо- прннятые во внимание при экспертиее ю подключен к выходу операционного бло- 1. Патент Франции h9 2086168, ка, при этом выход постоянной памятн кл. 9 06 Р 15/00, 1972. подключен ко второму входу регистра 2. Патент Великобритании М 1398367, мнкрокоманд, о т л и ч а ю щ н и с а кл. 9 4А, 1975 (прото гип).

Фиг.2

717773

Ооставитель А. Баранов

Редактор Н. Лобач ТехРед М. Келемеш Корректор Й. сутяга

Заказ 9849/67 Тиразс 751 Подписное

БНИИПИ Государственного комитета СССР но делай изобретений и открытий

113035, Москва, Ж 35, Раушскан наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4