Устройство для вычисления коэффициентов фурье

Иллюстрации

Показать всеРеферат

М. Д. Генкин, В. С. Голубев, А. Я. Куно, О. Б. Скворцов и. В. И. Шагур ин (72) Автори изобретения

Государственный научно-исследовательский институт (71) Заявитель машиноведения им, акад. А. А. Благонравова (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ ФУРЬЕ

Изобретение относится к области вычислительной техники и может быть использовано в цифровой аппаратуре для спектрального анализа радиотехнических и акустических сигналов, в высокоскоростных цифровых фильтрах, устройствах для вычисления корреляций и для вычисления коэффициентов Фурье. Известно устройство, в котором задача повьпп енин быстродействия решается за счетвычислення частичных сумм на четырех процессорах 1 .

Однако такое техническое решение позволяет повысить быстродействие лишь в 4 раза эа счет пропорйиональ ного увеличения объема аппаратуры. Кроме того, скорость вычислений оГраничена в атом устройстве быстродействием оперативного запоминаюшего устройства.

Наиболее близким техническим решением к данному предложению является устройство для вычисления коэффициентов, Фурье, содержащее аналог -цифровой преобразователь, информационный вход которого соединен со входом устройства, управляюший - с выходом первого гене памяти, где Я вЂ” количество коэффициентов Фурье, постоянный эапоминаюший блок, вход которого соединен с первым выходом блока управления, выход — с первой группой входов арифметического блока (2).

Данное устройство имеет память, состояшую из 1сфй блоков регистров сдвига. Первый блок состоит иэ К параллельно включенных регистров сдвига емкостью

° ° бит. каждая (К-раэрядность чисел).

Второй - из двух субблоков содержаших по К регистров емкостью - - бит и т.д. и

Последний блок содержит и субблоков по К одноразрядных регистров. Арифметическое устройство вычислителя имеет распределенную структуру и разбито на щЯ4арифметических устройств (АУ), каждое из которых обслуживает один блок памяти, причем, на входы каждого из AJ подаются операнды с выхода и входа соответствуюшего блока памяти и

717780

55 з значение вектора поворота, хранящегося в постоянном запоминающем устройстве (ПЗУ). Выбор необходимого значения вектора поворота,осуществляется с помощью устройства управления. Сдвиг информации в регистрах происходит с частотой аналого-цифрового преобразователя (AILH) при подаче на все регистры импульсов тактового генератора (ТГ) АБП.

Принцип действия вычислителя пред- io усматривает, что в течение первых

М тактов ТГ, когда заполняется первый блок памяти, все блоки АУ бездейк

К ствуют, далее, на протяжении — тактов работает лишь первый блок АУ, обра- iS батываюший отсчеты, содержащиеся в первом блоке памяти. Затем в течение тактов работают первый и второй блоки распределенного АУ и т.дв Все блоки АУ работают только в интервале 20 между отсчетами входной реализации с номерами M — 1 и М . Причем на этом интервале АУ выполняет порядка И операций умножения и сложения комплексных чисел, что ограничивает быстродей- 25 ствие устройства в реальном масштабе времени и требует значительных аппаратурных затрат. Таким образбм, недос- татком известного устройства является недостаточное быстродействие и значительное количество аппаратуры.:

Бель предлагаемого изобретения заключается в устранении указанных не- достатков, в увеличении быстродействия.

Бель изобретения достигается тем, 35 что устройство содержит второй генератор импульсов, первый и второй переключатели, группу буферных регистровр первый и второй коммутаторы и дешифратор, причем выход второго генератора 4О . импульсов подключен к первым входам первого и второго переключателя и первому управляющему входу арифметического блока, второй вход первого пере- ключателя соединен с выходом первого генератора импульсов, выход - e управляющим входом группы буферных регистров, информационных вход котброго сое динен с выходом аналогово-цифрового преобразователя, выход гр рппы буферных регистров соединен со входом первого регистра памяти, управляющий вход которого соединен с выходом второго переключателя, второй вход которого подключен к первому выходу дешифратора, BblxogbI регистров памяти

"оединены со входами первого коммута-.ора, управляющий вход которого соедиI

4 нен со вторым выходом блока управления, третий и четвертый выходы которого подключены соответственно к управляюшим входам дешифратора и второго коммутатора, вход блока управления соединен с первым выходом арифметического блока, второй выход которого соединен со входом второго коммутатора, выходы которого подключены к управляющим входам регистров памяти группы, информационные входы которых подключены к выходам дешифратора.

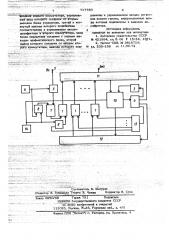

Структурная схема устройства вычисления коэффициентов Фурье дана на чертеже. Устройство содержит Bop N

/ групп регистров памяти 1, информационный вход устройства. - 2, постоянный запоминающий блок(ПЗБ) — 3, блок управления - 4, аналогово-цифровой преобразователь (АДП) — 5, первый генератор импульсов 6, группа буферных регистров - 7, переключатели 8, 9, арифметический блок 10, коммутаторы 11, 12, дешифратор 13, генератор импульсов 14.

Группа буферных регистров 7 и первая rpyrtna регистров памяти 1 имеют количество регистров, равное числу разрядов кода на выходе АДП. Вторая группа регистров памяти 1 имеет две группы регистров, каждая из которых также содержит количество регистров, равное раз рядндсти АБП, В третьем блоке таких групп - четыре, в четвертом 8 и т.д.

Блина буферных регистров и регистров первого блока памяти составляет М разрядов, причем, в регистрах первого блока имеется отвод от ячейки с номером и

Йлиив регистров второго блоки ф. третьего - - и т.д. и

Устройство работает следующим образом. Входная реализация в аналоговой форме непрерывно поступает на вход

АБП 5. С выхода AUDI 5 дискретные отсчеты с частотой первого тактового генератора 6. в параллельном коде загружаются в буферные регистры, переключатель 8 при этом обеспечивает подачу сигналов первого тактового генератора 6 на синхронизирующий вход группы буферных регистров 7. В тот момент, когда на-вход группы буферных регистров поступает отсчет с номером М, срабатывают переключатели 8 и 9 и синхронизирующие входы блока буферных регистров первого блока памяти подключаются к выходу второго тактового генератора

14, частота которого выбирается с таким

7177

10 разом производит операции с бранными, содержащимися в первом и втором блоках памяти, снимая соответствующие операнды с входов и выходов регистров;

При этом результат cràíäàðòíoé операции над данными первого блока заносится во второй блок, вытесняя хранящиеся в нем операнды, которые в свою очередь поступают на арифметическ пй блок. а

5 расчетом, чтобы в паузе между последним отсчетом предыдущей реализации и первым отсчетом последующей реализации содержимое группы буферных регистров 7 переписалось в первый регистр памяти 1.

После этого переключатель 8 вновь подключает синхронизируюшие входы блока буферных регистров 7 к выходу тактового генератора и этот блок готов к приему из АИП отсчетов следующей реализации. Одновременно переключатель

9 подсоединяет синхронизирующие входы первого блока 15егистроВ памяти 1 к выходу дешифратора 13, а блок управления формирует адрес коммутатора и ПЗБ, 15 соответствующие первым операндам для вычисления, На первом этапе вычислений адрес коммутатора соответствует выходам первого блока регистров памяти и отводам от их ячеек с номерами — .

14

2.

Ло

Указанные операнды подаются через коммутатор 11 на входы АУ, которое с высокой скоростью, обусловленной частотой генератора 14 выполняет стандарт ную операцию умножения одного из операндов на вектор поворота и сложения произведения с другим операндом. После выполнения стандартной операции на синхронизирующем выходе АУ 10 формируется импульс управления (КУ), сигна- З0 лизирующий о готовности АУ к следуюшей операции. Воздействием этого импульса

АУ генерирует адрес мультиплексора, соответствующий входам блока регистров памяти и адрес дешифратора 13, с вы- 35 хода которого поступает сигнал сдвига, на регистры второго блока памяти. Таким образом, в этот блок заносятся результаты вычислений арифметического блока. Одновременно БУ (4) формирует 40 адреса коммутатора 1 1 и П ЗБ 3, а также адрес дешифратора для сдвига информации в первом блоке памяти 1. После этого на вход арифметического блока 10 поступают операнды для выполнения сле- 45 дующей стандартной операции. Описанная процедура выполняется - - раз, пока не

t4 заполнятся регистры второго блока памяти. После этого АУ аналогичным об80

6 результат вычислений над ними заносится в третий блок. После N og N интеграций в регистрах последнего блока и:1-. пяти содержатся М коэффициентов Фурье, которые могут быть последовательно извлечены с частотой генератора 14 за время равное Гаузе между отсчетами входной реализации. При выборе элементной базы, обеспечивающей время умножения порядка 200 нс, Описанное устройство способно в реальном масштабе времени выполнять преобразования Фурье от 1024 точек за время порядка 2 мс.

Для того, чтобы получить такое быстродействие в устройстве — прототипе, при равной сложности арифметического устройства необходимо использовать элементы, обеспечивающие время умножения менее 10 нс, или пропорционально увеличить обьем аппаратуры в ЛУ.

Формула изобретения

Устройство для вычисления коэффициентов Фурье, содержащее аналоговоцифровой преобразователь, информационный вход которого соединен со входом устройства, управляющий — с выходом первого генератора импульсов,6+>N групп регистров памяти, где N — количество коэффициентов Фурье, постоянный запоминающий блок, вход которого сое-. динен с первым выходбм блока управления, выход — с первой группой входов арифметического блока, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит второй генератор импульсов, первый и второй переключатели, группу буферных регистров, первый и второй коммутаторы и дешифратор, причем выход второго генератора импульсов подключен к первым входам первого и второго переключателя и первому управляющему входу арифметического блока, второй вход первогб переключателя соединен с выходом первого генератора импульсов, выход — с управляющим входом группы буферных регистров, информационный вход которого соединен с выходом аналого-цифрового преобразователя, выход группы буферных регистров соединен со входами первого регистра памяти, управляющий вход которого соединен с выходом второго переключателя, второй вход которого подключен к первому вьФоду дешифратора, выходы регистров памяти соединены со

717780

f г:

Составитель B. Шагурин

Редактор Э. 1 убнйцкая Техред "Э. Чужик Корректор Н. Стец

Заказ 9850/68 Тираж 751 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., g. 4/5

Филиал ППП Патент„ r. Ужгород, ул. Проектная, 4

МГо мй ерйго ком утаМфЦ" уйраюа)о-, ший вход. которогб соедййей со вторым выходом блока управления, третий и четвертый выходы которого йодключены соответственно к упра щим входам дешифратора- и в%рого коммутатор, вхбд блока уйравленйя сЬединей с первым выходом арифметического блока, второй выход которого соединей со входом второго коммутатора, Mmодй "которого под8 ключенЫ к упрнавляюшим входам регист ров памяти группы, инфбрмационные вхо ды которых подключены к выходам дешифратора.

Источники информации, - -"прйФгМе во внимание при экспертизе

1. Авторское свидетельство СССР

Hs 421994, кл. 6 06 P 15/34, 1971.

2. Патент C1IIA % 3816729, 10 кл, 235-156 от 1 1. 06. 74