Следящая цифровая декада

Иллюстрации

Показать всеРеферат

ОП б А И Е

ИЗОБРЕТЕНИЯ (i t! 718%8

Саюа Сооетских

Социалистических

Республик

К АВТОРСКОМУ СВйДЕТЕЛЬСТВУ

61) Дополнительное к авт. свид-ву — (51) М. Кл з

Н ОЗК 13!18 (22) Заявлено 13.07,78 (21) 2650751 "18-21 с присоединением заявки №

Государстаеиный комитет (23) Приоритет (43) Опубликовано 28.02.80. Бюллетень № 8 (45) Дата опубликования описания 28.02.80 (53) УДК 681.325 (088.8) по делам изобретений и открытий (72) Автор изобретения

Я. В. Борис (71) Заявитель (54) СЛЕДЯЩАЯ ЦИФРОВАЯ ДЕКАДА

Изобретение относится к вычислительной технике.

Известна следящая цифровая декада, содержащая компараторы и источник эталонного напряжения (1).

Известна также следящая цифровая декада, состоящая из компараторов, одни из входов которых соединены с общей шиной, другие входы последовательно связаны с источником входного напряжения и с соответствующими входами делителя напряжения, подключенного к выходу источника эталонного напряжения, а выходы — с блоком логических элементов, соединенных с делителем напряжения (2).

Однако эти следящие декады имеют сложную схему преобразования.

Цель изобретения — повышение надежности устройства.

Указанная цель достигается тем, что в следящую цифровую декаду, содержащую источник эталонного напряжения, коммутатор, делитель напряжения, блок компараторов, блок логических элементов, введены дополнительный источник эталонного напряжения, дополнительный компаратор и ключ, причем выходы коммутатора соединены с первым входом ключа и через дополнительный- источник эталонного напряжения с вторым входом ключа и первым входом дополнительного компаратора, второй вход которого соединен с вторыми входами блока компараторов и общим входом блока логических элементов. Выход дополнительного компаратора соединен с управляющим входом блока логических элементов и управляющим входом ключа.

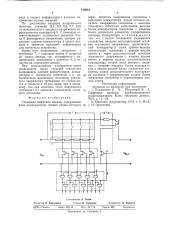

На чертеже показана структурная электрическая схема следящей декады.

Декада содержит блок 1 компараторов, ip коммутатор 2, делитель 3 напряжения, источник 4 эталонного напряжения, компаратор 5, блок б логических элементов, источник 7 эталонного напряжения и ключ 8.

Четыре прецизионных резистора, составляющих делитель 3, подключенный к источнику 4, подобраны таким образом, что на них создается напряжение, равное четным значениям (0,2; 0,4; О,б; 0,8) от максимального входного напряжения. Величина напряжения источника 7 выбрана равной 0,1 от максимального входного напряжения.

При входных напряжениях, превышающих четные значения (0,2; 0,4; О,б; 0,8) от максимального входного напряжения, срабатывает соответствующий компаратор блока 1 и подключает ключом коммутатора 2 своего разряда разностное напряжение между входным и напряжением на делителе 3 этого же разряда, подключенному

30 к источнику 4, к компаратору 5. Срабатывает логический элемент блока б этого раз718918

Составитель А. Титов

Корректор Л. Корогод

Техред В. Серякова

Редактор Е. Караулова

НПО «Поиск» Заказ 126/10 Изд. Кз 174 Тираж 995 Подписное

Типография, пр. Сапунова, 2 ряда и выдает информацию о входном напряжении четных значений.

11о достижении входным напряжением нечетных значений (0,1; 0,3; 0,5; 0,7; 0,9) от максимального входного напряжения опрокидывается компаратор 5. С помощью соответствующего логического элемента блока 6 формируется напряжение, которое управляет ключом коммутатора 2 своего разряда и является выходной информацией для отсчетного устройства.

Кроме того, напряжение, снимаемое с источника 7, с помощью ключа 8 подается на выход декады, где суммируется с напряжением, снимаемым с делителя 3, и подается на следующую декаду.

При использовании изобретения вдвое уменьшается число ступеней эталонного напряжения, ключей коммутаторов, компараторов и логических элементов, а к дополнительно введенному источнику эталонного напряжения требования по стабильности и точности в 10 раз ниже, чем к основному, так как величина этого напряжения составляет 0,1 значения напряжения основного источника.

Формула изобретения

Следящая цифровая декада, содержащая блок компараторов, первые входы которого через делитель напряжения соединены с выходами коммутатора, входы питания делителя напряжения соединены с выходом эталонного источника напряжения, выходы

5 блока компараторов соединены с входами блока логических элементов, управляющих ключами коммутатора, отличающаяся тем, что, с целью повышения надежности устройства, введены дополнительный источ10 ник эталонного напряжения, дополнительный компаратор и ключ, причем выходы коммутатора соединены с первым входом ключа и через дополнительный источник эталонного напряжения с вторым входом

15 ключа и первым входом дополнительного компаратора, второй вход которого соединен с вторыми входами блока компараторов н общим входом блока логических элементов, выход дополнительного компаратора соединен с управляющим входом блока логических элементов и управляющим входом ключа.

Источники информации, принятые во внимание при экспертизе

1, Блажкевич Б. И., Погребной В. Л.

Цифровые приборы комбинированного уравновешивания. Киев, «Наукова думка», 1973, с. 11 — 19, 2. Eiectrcnic Engineering, 1973, т. 9, № 15, ЗО с. 10 (прототип).