Устройство синхронизации по битам систем передачи цифровой информации

Иллюстрации

Показать всеРеферат

ея.„- „.

1 Д.: " " r - I (э, О П И С А Н И-Е

ИЗОБРЕТЕН И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< ) 718939

Ссюз Сееетских

Сеииалистических

Республик (61) Дополнительное к альт. свид-ву— (22) Заявлено 22.06.78 (21) 2634213/18-09 (51) М.Кл.2 Н 04 L7/04 с присоединением з,аявки №вЂ”

Гасударственный комитет (23) Приоритет— (43) Опубликовано 28.02.80, Бюллетень № 8 (45) Дата опубликования описания 28.02.80 па делам изобретений и открытий

, l (53) УДК 621.394.662 (088.8) С. Г. Муленко и A Г, Гончаров (72) Авторы изобретения (71) Заявитель . Всесоюзный заочный электротехнический институт связи (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО БИТАМ

СИСТЕМ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ

Изобретение относится к связи и может использоваться в системах передачи цифровой информации с использованием синхропоследовательностей, предшествующих информационным битам.

Известно устройство синхронизации по битам систем передач и цифровой информации, содержащее блок корреляторов, выходы которых подключены к входам блока вычитания, причем два соответствующих 10 выхода блока корреляторов подключены к входам сумматора, причем выходы генератора опорного сигнала подключены к дру; гим входам блока корреляторов и входам блока элементов И, а также пороговый 15 блок (1).

Однако известное устройство обладает значительной сложностью.

Целью изобретения является упрощение устройства путем уменьшения числа корре- 20 ляторов. .Для этого в устройство синхронизации по битам систе1м передачи цифровой информации, содержащее блок корреляторов, выходы которых подключены к входам блока 25 вычитания, прячем два соответствующих выхода блока корреляторов подключены к входам сумматора, причем выходы генератора опорного сигнала подключены к другим входам блока коррелятороВ и входам з0

2 блока элементов И, а также пороговый блок, введены блок памяти, блок дешифраторов, элемент ИЛИ, элемент И, триггер и выходной формирователь, причем выходы блока вычитания через последовательно соединенные блок памяти, блок дешифраторов, блок элементов И, элемент ИЛИ и элемент И подключены к входу выходного формирователя, а выход сумматора через последовательно соединенные пороговый блок и триггер подключен к другому входу элемента И, а другой выход триггера подключен к другому входу блока памяти.. -.-.:.- ..

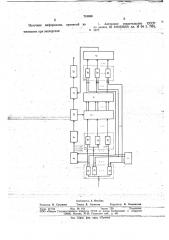

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство синхронизации по битам систем передачи цифровой информации содержит блок 1 корреляторов, блок 2 вычитания, блок 8 памяти, блок 4 дешифраторов, блок 5 элементов И, элемент ИЛИ б, генератор 7 опорного сигнала, сумматор 8, пороговый блок 9, триггер 10, элемент И

11. и выходной формирователь 12.

Кроме того, в блок 1 входят корреляторы 18, в блок 2 — компараторы 14, в блок

5 — элем енты И 15.

Устройство работает следующим образом. ЩФ ",-. -1I

718939 3 4 ./„

В исхбдном состояниями на вход устройст- " "ности; "а""зависит только оТ отношения сигва поступают обусловленные шумом"посыл- нал/шум в принимаемой синхропоследоваки со случайной длительностью и фазой. тельности, поэтому при достижении выходВыходные напряжения корреляторов 18 - ным -напряжением сумматора 8 определенблока 1, пропорциональные взаимнокорре- 5 його уровйя пороговый блок 9 вырабатываляционным функциям таких шумовых по- ет сигнал «1», который перебрасывает триг" сьйок и опорййх сйгйаЛов,-посТ йаюКйх" с гер 10 в единичное состояние. Выход едивыходов генератора 7, имеют малую вели- — ничного плеча триггера 10 управляет элечйну. " . — ментом И 11, который с этого момента наПри йоступленйи на. вход устройства ® чинает пропускать синхропоследовательсинхропоследовательнбсти на выходе каж- ность определенной фазы на вход выходнодого коррелятора 18 блока 1 начинает на- го формирователя 12, осуществляющего раСтать напряжение, "пропорцйональйое аб- формирование тактовых импульсов, аинхросолютной величине взаимнокорреляционной . низированных с началом каждого бита. фуйкции входной синхропоследовательности 15 С момента переброса триггера 10 в " и опорного колебанй3Г1 аййого коЯЙЙЙ%рa - едФИМное состояние выходной сигнал с

18. Велйчина вйхЬдйого напряжеййя "кор- . другого выхода триггера 10 (нулевое плерелятора 18 меняется в зависимости OT p3c- чо) управляет блоком 8, который запомисогласования по фазе бита привимаемои " нает записанный в нем код до конца сеанса синхропоследовательности и опорной син- 20 связи. По окончании сеанса связи триггер - " . ройосМф овайельностй"=даййого Ъоррелято- 10 перебрасывается в нулевое состояние и ра 18. Поскольку поступающие на корреля- устройство опять находится в ожидании торы 18 опорные колебания ймеют опреде- следующего сеанса связи. ленную задержку IIQ фазе бита относитель-:; .-:.:.,;-, но друг друга, то величины выходных на- 25 Таким образом до начала сеанса связи пряжений корреляторов 18 в зависимости обеспечивается режим когда устройство не от фазы бйта йрййимаемои сийхропоследо- вырабатывает тактовых импульсов, и тольвательноСти относительнб опорйого сигнал ко после накопления входного аигнала син меняются определенным образом, однознач- хропоследовательности, когда синхронный но соответствующим взаимным" задержкам 30 по фазе битов режим у станавливается с по фазе., . большой вероятностью, устройство генериВыходные напряжения соседних корре- рует тактовые импульсы, необходимые для ляторов 18 блока 1 сравниваются между со- приема цифровой информации. бой компараторами 14 блока Z, причем, если Предложенное устройство обеспечивает выходное напряжение 1-го коррелятора 18 35 возможйость получения высокой точности больше выходного напряжения i+1-го k6fi- "" синхройизации, помехоустойчивости m быстрелятора 18, то сравнивающий их компара- родействия при коротких синхропоследоватор 14 вырабатывает сигнал «1», а в про- тельностях. THB0IIoJIo2KHoM случае — сигнал «О». При изменении фазы бита входной синхройосле- 4О Фор мула из обр етенкя

"довательности отнооитЬЖйо первого бйорного-cHríàëà от 0 до Т на "вй6о7ГаМ КЯ а- Устройство синхройизации по битам сираторов 14 блока 2 вырабатываются соот- стем передачи цифровой информации со- - — Ъетствуйщие величине рассоглйсовайия дно- держащее блок корреляторов выходы кото " ичные парал.чельные коды; - — -;:;..=-,= .-:-:.:=-= -::;.= -..=:! . 45 рых подключены к входам блока вычи ания, :=..--:::-:=.:ы:;-:.--. .- .— --=-: -+--:- = ---:: --: --. —:"-"- - - — -- ":причем два соответствующих выхода блока

Эти коды поступают в блок 8, à него - - корреляторов подключейй к входам сумма

1 в блок 4, который определяет номер того —. тора, причем выходы генератора опорного элемента И 15 блока 5, который в данный: "сйгнала подключены к другим входам бломомент должен быть подключен к элемен- 5о ка корреляторов и входам блока элементов ту ИЛИ б.." " - :- " И, а также пороговый блок, отлич аюв щ ее ся т6м, что, с целью упрощения устНа входы элементов И 15 блока 5 по- ройства путем уменьшения числа коррелядаются опорные сигналы "с соответствую- торов, в него введены блок памяти, блок щих выходов генератора 7, различные по 55 дешифраторов, элемент ИЛИ, элемент "И, фазе бита в пределах от 0 до Т. В резуль- триггер и выходной формирователь, причем тате к входу элемента И 11 тодключается выходы блока вычитания через последоватот опорный сигнал, моменты смены сНМВо- "тельн о соединенные блок памяти блок делбв" B 3<0 )p6M, мйПйй ййо дЯМЙ7 М" бт " " "шифраторов блок элементов И элемент

Моментов смены символов во входнои син- ИЛИ и элемент И подключены к входу вы60

) ропоследовательй5с"гЁ. "" - : = — -=:=" ::= -" ходного формирователя а выход сумматора — через последовательйо "соединенные порого

Сумма выходных сигналов первого и N-to вый блок "и триггер подключен к другому корреляторов 18 блока 1 не зависит от фа- входу элемента И, а другой выход триггера зы.бита принимаемой синхропоследователь- 65 подключен к другому входу блока памяти.

718939

Составитель E. Петрова

Редактор Н. Суханова Техред В. Серякова Корректор И. Осиповская

Заказ 47/104 Изд. № 163 . Тираж 729 Подпйсное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж -35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патеичь

Источник информации, принятый во /

"внимание при экспертизе

1. Авторское свидетельство СССР по заявке № 2464638/09, кл. Н 04 L 7l04, 5 1977.