Цифровой интегратор

Иллюстрации

Показать всеРеферат

(11) 720427

Согоэ Советских

Социалистических

Республик

Оп ИСЛНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву (22) Заявлено 260276 (21) 2327397/18-24 с присоединением заявки 1)о— (23) Приоритет

Опубликовано 050380. Бюллетень Ì9 9

Дата опубликования описания - 050380 (5М)М. Кл.

G 06 J «1/02

Государственный комитет

СССР по делам изобретений и открытн и (53) УДК 681. 325 (088. 8) (72) Авторы изобретения

В.П. Данчеев, Н.С. Ермаков, Г.Я. Кузьмин и Е.Б. Смирнов (71) Заявитель (54) ЦИФРОВОР ИНТЕГРАТОР

Устройство относится к вычислительным устройствам систем управления и может быть использовано в системах численного программного управления различным технологическим оборудованием.

Известен интегратор (1), содержащий счетчик подынтегральной функции, счетчик тактовых импульсов и комбинационный блок, состоящий из элементов И-ИЛИ .

Недостатком устройства является то, что объем комбинационного блока увеличивается пропорционально числу его разрядов. 15

Наиболее близким техническим решением к изобретению является интегратор цифрового дифференциального анализатора (2), содержащий блок -2Q преобразования подынтегральной функции, первый элемент И, блок итераций, сдвиговый регистр, сумматор, первый вход которого подсоединен к выходу сдвигового регистра, пер- 25 вый выход — ко входу сдвигового регистра, второй выход — через элемент задержки к первому входу второго элемента И, подсоединенного выходом к второму входу сумг:;зтора, à 3р вторым входом к выходу блока итераГздостатком данного устройства является то, что объем блока преобразования подынтегральной функции увеличивается пропорционально числу его разрядов, что снижает надежность работы всего устройства.

Цель гзобретения — повышение, надежности работы интегратора.

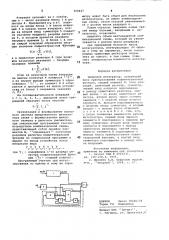

Поставленная цель достигается тем, что в предложенном устройстве первый вход первого элемента И подсоединен к первому выходу сумматора.

Второй вход первого элемента И подсоединен к выходу сдвигового регистра. Третий вход первого элемента И подсоецинен к выходу блока преобразования подынтегральной функции, а третий вход сумматора подсоединен к выходу блока итераций.

На чертеже представлена структурная схема интегратора.

Он содержит блок преобразования подынтегральиой функции 1, элемент

И 2, блок итераций 3, сдвиговый регистр 4, сумматор 5, элемент задер<ки б и элемент И 7.

Интегратор работает следующим

-Gpa=-ом.

720427

Формула изобретения итерация проходит за и тактов, где n - число разрядов блока 1 и регистра 4. Приращения 6 у и ь подаются на входы блока 1 И блока итераций 3 в первом такте итерации, когда на второй вход сумматора 5 подается значение младшего разряда регистра 4, в котором хранится значение текущего времени t. В блоке 1 в конце каждой итерации образуется текущее значение подынтегральной функции

\ f(H =:Е. л Y(e), k-j а в сдвиговом регистре 4 (при нулевом начальном значении) - текущее значение времени

В =Е. М, k.»

Если на некотором такте итерации ! 1 на выходе регистра 4 появился 0 26 а на первом выходе сумматора 5 obpaзовалась 1, то элемент И 2 отпирается и пропускает на выход устройства от блока 1 очередное значение ,7„(М .

На последовательности итераций

1, 2, 3, 4... выходной поток приращений образует поток частоты

rl !.

У=;Е Y Z

1»i

Организация и формирование выходного сигнала предложенного интегратора схожи с формированием выходного сигнала в двоичном умножнтеле, где специальный программный счетчик посредством комбинационной схемы, представляющей собой линейку элементов И, опрашивает состояние разрядов регистра подынтегральной функции по специальной программе и 40 выдает на выход устройства поток импульсов вида

1!! г ° ь г где 1 „- содержимое 1-го разряда регистра подынтегральной функции (Y1 — старший разряд) .

Программный счетчик при интегрировании по одному и тому же параметру может быть общим для нескольких интеграторов. Он имеет комбинационную схему, объем которой увеличивается с ростом числа разрядов и.

Таким образом, введение новых связей между блоками, входящими в интегратор, позволило! выделить объем нестандартной комбинационной схемы, который не увеличивается с ростом числа разрядов; при применении большого числа интеграторов, интегрирующих по одному и тому же параметру, число и-разрядных сдвиговых регистров сократить до одного, н тем самым, повы-сить аппаратурную надежность интегратора.

Цифровой интегратор, содержащий блок преобразования подынтегральной функции, первый элемент И,. блок итераций, сдвиговый регистр, сумматср, первый вход которого подсоединен к выходу сдвигового регистра, первый выход - ко входу сдвигового регистра! второй выход через элемент задержки — к первому входу второго элемента И, выходом подсоединенного к второму входу сумматора, а вторым входом — к выходу блока итераций, отличающийся тем, что, с целью повышения надежности работы интегратора, первый вход первого элемента И подсоединен к первому выходу сумматора; второй вход первого элемента И подсоединен к выходу сдвигового регистра; третий вход первого элемента И подсоединен к выходу блока преобразования подын— тегральной функции, а третий вход сумматора подсоединен н выходу блока итераций.

Источники информации, принятые во внимание при экспертизе

1. Патент США Р 2910237, кл. 135-150. 3, 1959.

2 . Шилейко А. B. Цифровые модели .

Y.— Л., Энергия, 1964, с. 27.

ЦНИИПИ Заказ 10220/34

Тираж 751 Подписное

Филиал ППП Патент, 1 г. Ужгород, ул. Проектная,4