Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< >720680

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 05.01.77 (21) 2442936/18-09 с присоединением заявки №вЂ” (23) Приоритет — (51) М. Кл

Н 03 D 3/04

Гееударстееллмк канитет

СССР до делам наебретений и еткрмтнй г (53) УДК 621.376.,55 (088.8) Опубликовано 05.03.80. Бюллетень №9

Дата опубликования описания 15.03.80 (72) Авторы изобретения

1О. К. Майоров и В. В. Афанасьев (71) Заявитель (54) ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к измерительной технике, может быть использовано для измерения разности фаз двух напряжений.

Известен фазовый дискриминатор, содержащий триггер, две трехвходовые схемы совпадения, инверторы входного и опорного сиг- 5 налов и сумматор; при этом два входа одной схемы совпадения соединены с источником входного сигнала и выходом инвертора опорного сигнала соответственно, третий ее вход соединен с прямым выходом триг гера, два входа второй схемы совпадения соединены с источником опорного сигнала и выходом инвертора входного сигнала соответственно (1).

Однако известный фазовый дискриминатор сложен и поэтому недостаточно надежен. >s

Цель изобретения — упрощение и повышение надежности схемы.

Для этого в фазовом дискриминаторе, содержащем триггер, две трехвходовые схемы совпадения, инверторы входного и опорного сигналов и сумматор, причем два sxoда одной схемы совпадения соединены с источником входного сигнала и выходом инвертора опорного сигнала соответственно, третий ее вход соединен с прямым выходом триггера, два входа второй схемы совпадения соединены с источником опорного сигнала и выходом инвертора входного сигнала соответственно, третий ее вход совпадения соединен с инверсным выходом триггера, выходы схем совпадения подключены ко входам сумматора, а входы триггера под- ключены к выходам двух дополнительно вве-"денных схем совпадения,— два входа каждой из которых соединены с выходами инверторов входного и опорного сигналов, а третьи входы подключены к источнику -входного и опорного сигналов соответственно.

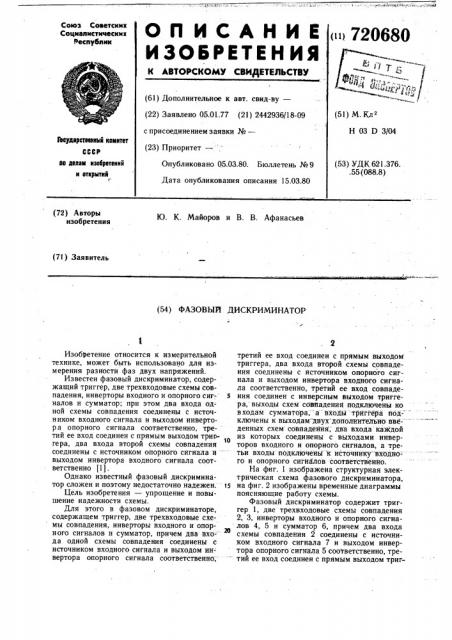

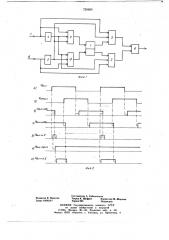

На фиг. 1 изображена структурная электрическая схема фазового дискриминатора, на фиг. 2 изображены временные диаграммы поясняющие работу схемы.

Фазовый дискриминатор содержит триггер 1, две трехвходовые схемы совпадения

2, 3, инверторы входного и опорного сигналов 4, 5 и сумматор 6, причем два входа схемы совпадения 2 соединены с источником входного сигнала 7 и выходом инвертора опорного сигнала 5 соответственно, третий ее вход соединен с прямым выходом триг720680 гера 1. Два входа схемы совпадения 3 соединены с источником опорного сигнала 8 и выходом инвертора входного сигнала 4 соответственно, третий ее вход соединен с инверсным выходом триггера 1. Выходы схем совпадения 2, 3 подключены ко входам сумматора 6, а входы триггера 1 — к выходам двух дополнительно введенных схем совпадения 9, 10 два входа каждой из которой соединены с выходами инверторов входного и опорного сигналов 4, 5, а третьи входы подключены к источнику входного 7 и опорного 8 сигналов соответственно.

Фазовый дискриминатор работает следующим образом.

Предположим, что напряжение входного сигнала (рис. 2а) опережает по фазе напряжение опорного сигнала (рис. 26).

При переходе напряжения входного сигнала с низкого уровня на втором входе схемы совпадения 9 некоторое время, обусловленное инерционностью инвертора входного сигнала 4, присутствует напряжение на высоком уровне (фиг. 2в), поэтому на выходе схемы совпадения 9 появляется короткий импульс (фиг. 2г). Импульс со схемы совпадения 9 (рис. 2г) поступает на вход триггера 1 каждый раз при переходе напряжения входного сигнала с низкого уровня на высокий. Этот импульс переводит триггер 1 в состояние, при котором на его выходе, соединенном со входом схемы совпадения 2, будет высокий уровень напряжения (фиг. 2е

При переходе напряжения опорного сигнала с низкого уровня на высокий (рис. 26), на выходе схемы совпадения 10 импульсов нет, так как в эти моменты времени, обусловленные инерционностью инвертора опорного сигнала 5, напряжение на его выходе И находится на низком уровне (рис. 2д). Следовательно, триггер 1 находится постоянно в одном состоянии. При этом на выходе схемы совпадения 2 каждый период появляются импульсы (рис. 2ж), длительность которых пропорциональна фазовому сдвигу между входными напряжениями фазового дискриминатора.

Когда триггер 1 находится в одном состоянии, схема совпадения 3 постоянно закрыта. 4S

Если в некоторый момент времени напряжение входного сигнала отстает по фазе от напряжения опорного сигнала, триггер 1 изменяет свое состояние, схема совпадения 2 закрывается, и на выходе схемы совпадения 3 появляются импульсы напряжения, длительность которых пропорциональна разности фаз входных напряжений фазового дискриминатора.

Напряжение на выходе сумматора 6 пропорционально длительности импульсов, подаваемых на его вход, а полярность этого напряжения зависит от того, на какой вход сумматора подаются импульсы напряжения.

Следовательно, напряжение на выходе сумматора пропорционально сдвигу фаз между напряжениями входного и опорного сигналов, а его полярность зависит от знака разности фаз этих сигналов.

Таким образом, данный фазовый дискриминатор при одинаковых параметрах проще прототипа, поскольку содержит один триггер, а не два: в связи с этим повышается его надежность.

Формула изобретения

Фазовый дискриминатор, содержащий, триггер, две трехвходовые схемы совпадения, инверторы входного и опорного сигналов и сумматор, при этом два входа одной схемы совпадения соединены с источником входного сигнала и выходом инвертора опорного сигнала соответственно, третий ее вход соединен с прямым выходом триггера, два входа второй схемы совпадения соединены с источником опорного сигнала и выходом и нвертора входного сигнала соответственно, отличающийся тем, что, с целью его упрощения и повышения надежности, третий вход второй схемы совпадения соединен с инверсным выходом триггера, выходы схем совпадения подключены ко входам сумматора, а входы триггера подключены к выходам двух дополнительно введенных схем совпадения, два входа каждой из которых соединены с выходами инверторов входного и опорного сигналов соответственно.

Источники информации, принятые во внимание при экспертизе . Авторское свидетельство СССР № 416817, кл. Н 03 Р 3/04, 1972.

720680

Фиг.1

Ьх,c

a) (!

1 г)

° Ьысииб р) Фы.г сто

1 ) 8

Ьык. mp,й) Ьы.г с».2

1 фиг. 2

Редактор Ф.Федотов

Заказ 19243 47 опар. с

b)

1 ю)

03ьк.иихф

Составитель А. Заболотская

Техред К. Шуфрич Корректор М. Шароши

Тираж 995 Подписное

ЦН И И П И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4