Формирователь импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ .

Союз Советских

Социалистических

Республик

„,720709 (6! ) Дополнительное к авт. свид-ау(22) Закалено 16.02.78 (21) 2579944/18-21 с присоединением заявки Ж (51)M. Кл.

Н 03 К 5/04

Гасударственный каннтет

СССР (23) Приоритет(Опубликовано 05.03.80. Бюллетень № 9 на делан нзабретеннй и аткрнтнй (53) УД К 621.374. .387(088.8) Дата опубликования описания 18.03.80 (72) Авторы изобретения

В. М. Матющевский, Л. С. Морщенок и Ю. П. Тюнин (7!) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к телеавтоматике и вычислительной технике и может быть использовано в устройствах дискретной обработки информации.

Известно устройстао, формирующее импульсы по переднему и заднему фрон 5 там входного сигнала (1) .

Недостаток данного устройства заключается в том, что формируемые импульсы "не привязаны" к опорной тактоt0 вой частоте, синхронизирующей работу всего устройства обработки информации.

Известно устройство для формирования импульсов по фронту и спаду входного сигнала, содержащее ))-триггер и схему исключающее ИЛИ" 2).

Недостаток данного устройства — уз-. кая область применения вследствие того, что длительность формируемых выходных импульсов мала, так как она определяет-" ся только собственной зацержкой пере1 ключения триггера, кроме того, выходные импульсы "не привязаны" к опорной тактовой частоте, синхронизирующей ра2 боту всего устройства обработкп информациии.

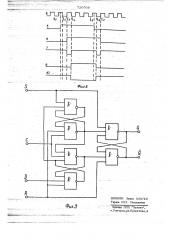

С целью расширения функциональных воэможностей, в устройство, содержащее

Ь-триггер, введены второй 1)-триггер и два инвертора, причемП -входы обоих триггеров соединены с тттиной входного сигнала, вход синхронизации второго триггера соединен с шиной тактовых импульсов и через первый инвертор — с входом синхронизации первого триггера, единичный выход которого соединен через второй инвертор г входом установки в "1 второго триггера, единичный выход Второго триггера подсоединен к входу установки в 0 первого триггера, нулевой выход которого подсоединен к входу установки в О второго триггера.

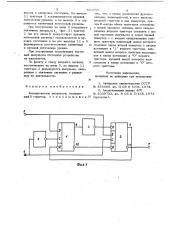

На фиг. 1 представлена схема уст ройства; на фиг. 2 — временная диаграмма его работы; на фиг. 3 — схема D -триггера, поясняющая принцип его работы.

Устройство содержит D --трпгг еры 1, 2, первый инвертор 3, второй инаертбр 4, 7207 шину 5 входных импульсов, шину 6 тактовых импульсов, выходную шину 7. Рди 1ичные выходы D -триггеров обозйачены цифрами 8 и 9, а нулевые — 10 и 11.

D-входы триггеров 1 и 2 соединены с

5 шиной 5 входных импульсов. Шина тактовых импульсов соединена со входом

С триггера 2 и через инвертор 3 со входом С триггера 1, единичный выход 8 кс" торого соединен через инвертор 4 со вхо- 1о дом 6 -триггера 2. Единичный выход 9 триггера 2 соединен со входом R-триггера 1, нулевой выход 10 которого соединен со входом R-триггера 2. Нулевой выход 11 триггера 2 соединен с выход- is ной ш иной 7.

Э -триггер содержит информационный

D -âõîä, вход С синхронизации, вход 5 установки в "1" (состояние, при котором на единичном выходе Q установлен еди- 2о ничный логический уровень вход R установки в "О .

Устройство работает следующим образом.

В"исходном состоянии на шине 5 присутствует нулевой логический уровень, на шину 6 поступают тактовые импульсы.

На выходе инвертора 3 формируются импульсы, инвертированные по отношению к импульсам, поступающим на шину 6. На 30 единичных выходах 8, 9 триггеров присутствуют нулевые логические уровни (вследствие того, что на9-входы этих триггеров поступает нулевой логический уровень). На входах.5 и R триггера 2 35 присутствуют единичные логические уровйи. На входе R-триггера 1 присутствует нулевой логический уровень, удерживающий триггер 1 в нулевом состоянии.

Пусть в момент времени t, (фиг. 2) 4о на шине 6 присутствует тактовый импульс (единичный логический уровень), на шину 5 поступает единичный логический уровень. При этом состояние триггера 1 из-1 мениться не может, так как он "блокирован 45 нулевым логическим уровнем, поступающим на его вход 9. Состояние триггера 2 также не изменяется, так как он может изменить свое состояние только по переднему фронту тактового импуль- Ю са.

При окончании тактового импульса 1 (фиг. 2) состояние триггеров 1 и 2 по

" уже указанным причинам также не изменяется.

Прн поступлении на шину 6 следующего тактового импульса ((фиг. 2) триггер 2 (на его входе D присутствует еди09 4 ничный логический уровень) переключается в едиш1чное состояние и на его выходах 9 и 11 формируются соответственно единичный и нулевой логические уровни.

Единичный логический уровень с выхода 9 триггера 2 поступает на вход триггера 1 в результате чего прекращается "блокировка" триггера 1, то есть триггер 1 подготовлен к работе. При окончании тактового импульса д (фиг. 2) на входе

С триггера 1 формируется единичный логический уровень и триггер 1 (на его входе Ъ присутствует единичный логический уровень) переключается в единичное состояние. На выходе 10 триггера 1 и выходе инвертора 4 формируются нулевые логические уровни, поступающие на оба установочных входа б и R-триггера 2. B результате на выходе 9 триггера

2 сохраняется, а на выходе ll формируется единичный логический уровень.

При поступлении следующих тактовых импульсов состояние устройства не изменяется — состояние триггера 1 соответствует состоянию его информационного Э -входа. а триггер 2 "блокирован"

1 нулевыми логическими уровнями,- поступающими на его входы S u R.

В момент времени t< (фиг. 2), когда на шине 6 присутствует тактовый импульс, на шину 5 поступает нулевой логический уровень. Состояние устройства при этом не изменяется.

При окончании тактового импульса (фиг. 2) на входе С триггера 1 формируется единичный логический уровень и триггер 1 (на его входе 0 присутствует нулевой логический уровень) переключает. ся в нулевое состояние. На его выходах

10 и 8 формируются соответственно единичный и нулевой логические уровни. В результате, на обоих установочных входах R и 5-триггера 2 формируются единичные логические уровни.

Единичный логический уровень на входе 5-триггера 2 устанавливается позднее, чем на его входе R. Это объясняется, во-первых, собственной задержкой

1 инвертора 4,и, во-вторых, тем, что для триггеров, выполненных на схеме И-HE (см. фиг. 3), задержка переключения из единичного состояния в нулевое больше, чем задержка переключения из нулевого

10 01 состояния в единичное (t > t ) . .Вследз э ствие того, что нулевой логический уровень "снимается" со входа 5 (входа установки в 1 ) триггера 2 позднее, чем с его входа R, то триггер 2 устанавли5 720 веется в единичное состояние. На выходе.

11 триггера 2 устанавливается нулевой логический уровень, а на выходе 9 - сохраняется единичный логический уровень.

При поступлении на шину 6 очередного тактового импульса (фиг. 2) триггер ч

2 (на его входе b присутствует нулевой логический уровень) переключается в нулевое состояние и на его выходах 11 и 9 формируются соответственно единичный > o и нулевой логические уровни.

При поступлении последующих тактовых импульсов состояние устройства не изменяется.

По фронту и спаду входного сигнала, 15 поступающего на шину 5, на выходе 11 триггера 2 формируются импульсы, синхронные с тактовым сигналом и равные ему по длительности.

Формула изобретения

Формирователь импульсов, содержащийЬ-триггер, отличающийся

709 6 тем, что, с целью расширения функциональных возможностей, в него введены второй Э -триггер и два инвертора, причем0-входы обоих триггеров соединены с шиной входного сигнала, вход синхронизации второго триггера соединен с шиной тактовых импульсов и через первый инвертор — с входом сйнхронизапии пер- вого триггера, единичный выход которого. соединен через второй инвертор с входом установки в "1 второго триггера, единичный выход второго триггера подсоединен к входу установки в "О первого триггера, нулевой выход которого подсоединен к входу установки в "О" второго триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 455468, кл. Н 03 К 5/04, 1974.

2. Акцептованная заявка ФРГ

¹ 2039732, кл. Н 03 К 5/156, 1973 (прототип).

720709

45) Ч 6) Г ,) )

)

)) !

) ((I

)! ) фи.г.Л

Ш1ИИЛИ Заказ 345/19

Тираж 995 Подписное

Филиал ППП Патент", г.Уха ороп,ул.Проектная,4