Согласованный фильтр сложных сигналов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (iiI 720736 (ю

t. f (/ (k

1 (61) Дополнительное к авт. свид-ву (51)М. Кл.

Н 04 В 3/06

Н 04 В 1/10 (22) Заявлено17.07.78 (2l ) 2645257/18-09 с присоеаинениехт заявки М (23 ) Приоритет

Опубликовано 05.03.80. Бюллетень №9

Гесударстеен ьй кемнтет

СССР по делен нзебпетеннй н открытка (») ЯК 621.391..8(088.8) Дата опубликования описания 07.03.80 (72) Авторы изобретения Г. И. Тузов, В. В. Горшков и В. И. Прытков (73) Заявитель (54) СОГЛАСОВАННЫЙ ФИЛЬТР СЛОЖНЫХ СИГНАЛОВ

Изобретение относится к системе свя- зи и управления и может быть использовано для согласованной фильтрации сложных сигналов.

Известен согласованный фильтр сложных сигналов, содержащий первый и вто5 рой элементы памяти, генератор и перемножитель fl) .

Однако известный согласованный фильтр сложных сигналов обладает низкой точ-

10 костью согласования входного сигнала с импульсной характеристикой согласован ного фильтра.

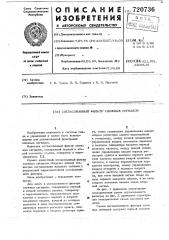

Бель изобретения — повышение точности, Для этого в согласованном фильтре сложных сигналов, содержащем первый и второй элементы памяти, генератор, и перемножитель, перемножитель подключен к выходам первого и второго элементов памяти, каждый из которых выполнен в виде последовательно соединенных первого регистра сдвига, элемента переписи и второго регистра сдви, ra,. точка соединения управляющих входов вторых регистров сдвига подсоединена к генератору, между точкой соединения управляющих входов элементов переписи и выходом геиератора включен первый делитель частоты, между точкой соединения управляющих входов первых р гистров сдвига и выходом первого дели-. теля частоты включен второй делитель частоты, к выходу перемножителя подключен интегратор, между управляющим входом которого и выходом второго делителя частоты включена линия задержки, при этом входной сигнал подан на вход первого элемента памяти, а на вход второго элемента памяти подан опорный сигнал.

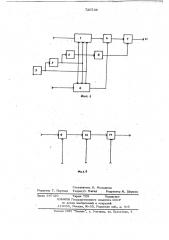

На фиг. 1 приведена структурная электрическая схема согласованного фильтра", на фиг. 2 приведена структурная электрическая схема элемента памяти.

Схема согласованного фильтра слож ных сигналов содержит первый элемент

720736 4 ся отсчеты корреляционной функции. Импульсы со второго делителя 6 частоты осуществляют также сброс интегратора

7.

Параметры согласованного фильтра а. выбираются таким образом, чтобы все операции считывания содержимого пер» вого элемента 1 памяти и второго элемента 2 памяти, перемножения считанf0, ных отсчетов, накопления отсчетов в интеграторе 7, выдачи отсчетов корреляционной функции и сброс интегратора

7 завершились до поступления следующего синхроимпульса переписи.

Фор мула изобре тения

3

1 памяти, второй элемент 2 йамяти, генератор 3, перемножитель 4, первый делитель 5 (частоты, второй делитель

6 частоты, интегратор 7, линию задерж ки 8, первый регистр 9 сдвига, "элемент

10 переписи и второй регистр 11 сдвиг

Устройство работает следующим образом.

Отсчеты принимаемого сйгнала заносятся в первый элемент l памяти. От — счеты опорного сигнала заносятся во второй элемент 2 памяти.

Первый регистр 9 и второй регистр

l1 могут быть выполнены, например, в виде цифровых регистров, каждый разряд которых представляет собой ячейку памяти для хранения отдельного предварительного квантованного отсчета.

При поступлении синхронмпульса записи на вход первого регистра 9 производится продвижение информации на один разряд со стиранием отсчета, который хранился до этого в старшем разряде, и занесением нового отсчета в младший разряд. При поступлении син- кроимпульса на вход переписи sneMeнта

10 происходит параллельное неразрушающее считывание содержимого первого регистра 9 и перепись этого содержимого через элемент 10 переписи во второй регистр ll, При поступлении синхроимпульсов на вход считывания второго регистра

11 происходит последовательное считывание занесенных во второй регистр l 1 отсчетов с последующей очисткой каждого разряда. Ге- З5 нератор 3, первый делитель 5 частоты и второй делитель 6 частоты предйазначены для формирования импульсов управления записью, перезаписью и считыванием информации в первом элементе 1 памяти 40 и втором элементе 2 памяти.

Информация с выхода первого элемента 1 памяти перемножается с информацией второго элемента 2 памяти на перемножителе 4 и интегрируется на ин- 4> теграторе 7. С выхода второго делителя 6 частоты через линию задержки 8 на интегратор 7 поступают импульсы опроса. На выходе интегратора 7 образую

Согласованный фильтр сложных сиг-. налов, содержащий первый и второй элементы памяти, генератор и перемножитель, отличающийся тем, что, с целью повышения точности, перемножитель подключен к выходам первого и. второго элементов памяти, каждый из которых, выполнен в виде последовательно соединенных первого регистра сдвига, элемента переписи и второго регистра сдвига, точка соединения управляющих входов вторых регистров сдвига подсоединена к генератору, между точкой соединения управляющих входов элементов переписи и вы ходом генератора включен первый делитель частоты, между точкой соединения управляющих входов первых регистров сдвига Й выходом. первого делителя частоты Включен второй делитель частоты, к выходу перемножителя подключен интегра-, тор, между управляющим входом которого и выходом второго делителя частоты включена линия задержки, при этом входной сигнал подан на вход первого элемента памяти, а на вход второго элемента памяти подан опорный сигнал.

Источники информации, принятые во внимание при экспертизе

1. Тузов Г. И. Статистическая теория приема сложных сигналов, Советсткое радио, 1977, с. 114, рис. 3.6 (прототип).

720736

Составитель Н. Мельников

Редактор Т. Портная Техред C. Мигай Корректор Я. Шароши

Заказ 347/20 Тираж 729 Подписное

UHHHfIH Государственного комитета СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4