Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

И 3 O S P Е и Е n H S < 720767

Союз Советских

Социалистических

Республик вптБ

1 (51)М. Кл.2

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлвно 31,0778 (21) 2662634/18-09 с присоединением заявки М (23) Приоритет

Опубликовано 050380 Бюллетень М 9

Дата опубликования описания 08.0380

Н 04 1 7/08

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621.394. .662 (088.8) (72) Автор изобретения

A . А. Ротарь (71) Заявитель (54) УСТРОЙСТВО TAKTOBOA СИНХРОНИЗАЦИИ

Изобретение относится к технике передачи данных и может использоваться в автоматизированных системах для синхронного приема. 5

Известно устройство тактовой син- хронизации, содержащее задающий генератор, блок добавления-вычитания, соответствующий вход которого соединен с выходом сумматора, делитель, 10 первый преобразователь, блок управления, демодулятор (1) .

Однако такое устройство имеет невысокую скорость вхождения в синхронизм. 15

Цель из обрете ни я — уменьшение в ремени вхождения в синхронизм. для этого в устройство тактовой синхронизации, содержащее задающий генератор, блок добавления-вычитания, 20 соответствующий вход которого соединен с выходом сумматора, делитель, первый преобразователь, блок управления, демодулятор, введены блок памяти и последовательно соединенные пер- 25 вый счетчик, второй преобразователь и второй счетчик, причем выход задающего генератора через последовательно соединенные блок добавления-вычитания, делитель, блок Памяти, первый преобразователь и сумматор подключен к входу первого и другому входу второго счетчика, а выход второго счетчика подключен к второму входу блока добавления-вычитания, третий вход которого соединен с выходом делителя, вторым входом сумматора и входом блока управления, другой вход которого соединен с выходом демодулятора, а выход блока управления подключен к другим входам блока памяти и первого счетчика и третьему входу сумматора, при этом третий вход второго счетчика подключен к другому входу блока добавления-вычитания.

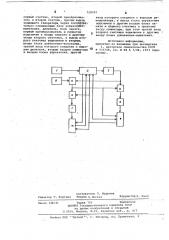

На чертеже дана структурная электрическая схема устройства.

Схема устройства содержит задающий генератор 1, делитель 2, блок 3 добавления-вычитания, сумматор 4, демодулятор 5, блок 6 управления, преобразователи 7,8, счетчики 9, 10 и блок 11 памяти.

Устройство работает следующим образом.

С задающего генератора 1 через блок 3 импульсная последователь н.:c Tb делится делителем 2 в N раз. П)>п

720767 этом состояния делителя 2 0 < n(--1

2 задают зону опережений; а" состбя ния

c n N — 1 зону отСтавания.

С демодулятора 5 сигнал поступает 5 в блок 6 управления. В зоне опережения по каждому значащему моменту сигнала блок 6 дает команду в блок 11 памяти на запись состояния делителя 2 (величину фазы опережения) . При переходе делйтеля 2 в состояние N/2, если

";в s»oNy- опенке»жения йо»пал-хотя бы о»дйн значащий момент, блок 6 дает -команду в сумматор 4 принять с блока 11 через преобра зов атель 8 в еличйну рас- 1 5 согласования фаз. Состоянием делителя

2 в момент -передачи величины» р»аСсогла. сования фаз в сумматор 4 задается знак этого рассогласования.

Для преобразователя 8 функцию 2О у = f(х) преобразования входной величины Х в выходную величину Y задают нелинейно убывающей. Пбэтому сумматор 4 совместно с Преобразователем 8

-эквивалентен сумматору с переменной емкостью, т. е. с возрастанием величи йы, эаписай» ной в блоке 11, растет емкость эквивалентного сумматора. Такое свойство э»квивалентйог»о сумматора позволяет уменьшить емкость сумматора 4 без потери помехоустойчивости при больших случайных отклонениях эйачащих МоМВНТОВ и повысить скорость синхронизации.

В зоне отставания по первому значащему моменту сигнала блок 6 управ ления дает команду в блок 11 на эайись состояния делителя 2 (величину фазы отставания) .

Такая.фиксация величин рассогласования фаз, т.е. определение фазы 40 первого значащего момента относительно середийы" единичйогo ййте»"рвала, определенной устройством как в сторону -отставания, так и в сторону опережения, лозволяет исключить дробленый участок сигнала иэ зоны измерения, что также дает повышение псме»хоубтбйчивости работы устройства.

При переходе делителя 2 в состоя-, ние 0, если в эбну отставания по пал хртя бы одни значащий момент, блок 6 дает команду в сумматор 4 йри нять с блока 11 через преобразователь. 8 величину рассогласования фаз.

Если в зоне отставания (опережения) был зафиксирован блоком 6 управления хотя бы один зйач»ащи»й момент, то этот блок 6 передает единичный им-пульс на вход счетчика 9 для подсче та "числа произведенййх иэмерейй»й в е=" лйчин» ы расс о»гласов ания "фа з, вызнав - " О ших переполнение сумматора 4 с ем« костью С.

При переполнении "сумматора 4 передаетсй знак переполнения в блок 3, - к анда перезаписи числа B счетчик!

10 из счетчика 9 через преобразователь 7 и сигнал установки счетчика 9 в 0

Для преббразователя 7 функцию х -А(у) преобразования входной величины Y в выходную величину Х задают обратной по отношению к функции преобразователя 8. Так, если

С = у, то х А —

1)cl

t=),» и где у. — преобразованная величина

S рассогласования фаз j-го замера;

Х, — среднее значение рассогласования фаз.

Состояние счетчика 10 передается на вход блока 3, который с учетом знака расфазировки, задаваемого сумматором 4, производит добавление (вычитайие) импульсов на входе делителя 2 к (от) периодической их последовательности с задающегo генератора 1.

При этом каждый добавленный (вычтенный) импульс к (от) входной последовательности импульсов делителя 2 вычитается из счетчика 10. 3а один период работы делителя 2 число добавленных (вычтенных) импульсов зависит бт величины Х счетчика 10 и может менйться от максимального шага подстройки, зависящего от заданной полосы синхронизации, до нуля при

Х вЂ” О. Моменты корректировки фазы задаются блоку 3 состоянием делителя

2, а решение о проведении этой Корректировки принимается в зависимости от состояния счетчика 10, т.е. от величины Х р .

Счетчик 9 и преобразователь 7 позволяют получить количественную оценку рассогласования фаз, а счетчик

10 — нормированную корректировку этой фазы за единичный интервал. На краю полосы синхронизации до получения следующей оценки Xcpj w< корректировка фазы будет проведена на всю величину Xcp.j или на значительную ее часть, что- ускоряет процесс синхрони-. зации, ослабляет зависимость полосы

его удержания от изменения скважности телеграфного сигнала, при этом полоса удержания расширяется беэ потери помехоустойчивости.

Формула изобретения

Устройство тактовой синхронизации, содержащее задающий генератор, блок добавления-вычитания, соответствуюший вход которого соединен с выходом сумматора, делитель, первый преобразователь, блок управления, демодулятор, отличающеес я тем, что, с целью уменьшения времени вхождения в синхронизм, введены блок па мяти и последовательно соединенные

7207б7

Составитель Т. Маркина

Редактор Т, Портная Техред O,Пегеза КорректоР Е. Папп

Тираж 729 Подпис ное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раумская наб., д. 4/5

Заказ 348/21 I

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 первый счетчик, второй преобразователь и второй счетчик, причем выход задающего генератора через посМ63 овательно соединенные блок добавле Ий - . вычитания, делитель, блок памяти, первый преобразователь и сумматор подключен к входу первого и другому входу второго счетчика, а выход второгь счетчика пЬдключен" к втОфом1 входу блока добавления-вычитания, третий вход которого соединен с выходом делителя, вторым входом сумматора ® и входом блока управления, другой вход которого соединен с выходом демодулятора, а выход блока управления подключен к друт им входам блока памяти и первого счетчика и третьему входу сумматора, при этом третий вход второго счетчика подключен к другсиу входу блока добавления-вычитания.

Источники информации, принятые во внимание при зкспертиэе

1. Авторское свидетельство СССР

Р 535748, кл. Н О4 L 7/04, 1973 (прототип) °