Устройство для синхронизации дискретных сигналов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (72OZeS

ИЗОБВЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

I (61) Дополнительное к авт. свид-ву— (22) Заявлено 31.01.78 (21) 2575797/18-09 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 05.03.80. Бюллетень №9

Дата опубликования описания 15.03.80 (51) Я. Клз.

Н 04 L7/10

Гооударстаеииый комитет по пелен изобретений и открытий (53) УДК 621.394. .662.2 (088.8) (72) Авторы изобретения

Э. И. Бауман, Ю. Л. Лейзен и М И. Ривман (7l ) Заявитель (54) УСТРОЯСТВО ДЛЯ СИНХРОНИЗАЦИИ

ДИСКРЕТНЫХ СИГНАЛОВ

Изобретение относится к радиотехнике.

Известно устройство для синхронизации, . содержащее последовательно соединенные генератор импульсов и делитель частотыи последовательно соединенные RS-триггер управления и первый элемент И, а также второй элемент И (1).

Однако в известном устройстве значительно время вхождения в синхронизм.

Цель изобретения — сокращение времени вхождения в синхронизм.

Для этого в устройство для синхронизации дискретных сигналов, содержащее последовательно соединенные генератор импульсов и делитель частоты и последовательно соединенные RS-триггер управления и первый элемент И, а также второй элемент

И, введены последовательно соединенные первый элемент ИЛИ и элемент запрета, а также второй элемент ИЛИ, два дополнительных RS-триггера и два элемента ИЛИНЕ, при этом выход элемента запрета подключен к S-входу RS-триггера управления, выход которого подключен к одному из входов второго элемента И, к двумя другим входам которого подключены соответственно выход делителя частоты, объединенный с соответствующим входом первого элемента

ИЛИ, и выход второго элемента ИЛИ-НЕ, ко входу которого подключен выход первого дополнительного RS-триггера, к S-входу которого подключен выход первого элемента И, к двум другим входам которого подключены соответственно соответствующий выход делителя частоты, объединенный с соответствующим входом первого элемента

ИЛИ, и выход первого элемента ИЛИ-НЕ, ко входу которого подключен выход второго дополнительного RS-триггера, к S-входу которого подключен выход второго элемента

И, а выходы первого и второго элементов И подключены ко входам второго элемента ..--..--.-.

ИЛИ, причем на R-входы RS-триггера управления, первого и второго дополнительных

= RS-триггеров и на соответствующий вход первого элемента ИЛИ подана последовательность импульсов, соответствующих передним фронтам кодовых символов входного сигнала, а на сигнальный вход элемента,.-.-запрета подан информационный сигнал.

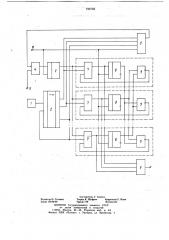

На чертеже изображена структурная электрическая схема предлагаемого устройства.

0768

/.

Устройство содержйт генератор 1 Импульсов, делитель частоты 2, RS-триггер 3 управления, элемент запрета 4, элементы ИЛИ 5 и 6, элементы И 7, RS-триггеры 8; элементы

ИЛИ-НЕ 9..

Устройство работает следующим образом.

На выходах делителя частоты 2 формируются две последовательности неперекрывающих импульсов, сдвинутых один относительно другого на 180 . Импульс, соответствующий переднему фронту кодового символа, устанавливает RS-триггер 3 управления и RS- триггеры 8 в нулевое состояние, и одновременно, пройдя через элемент ИЛИ

5, запрещает поступление через элемент запрета 4 кодового символа íà S-вход RSтриггера 3 управления, что обеспечивает надежное обнуЛение этого триггера. Если к моменту окончания импульса на входе 10 устройства сигналов на обоих выходах делителя 2 частоты нет, то с окончанием этого импульса запрет с выхода элемента ИЛИ 5 на вход элемента запрета 4 снимается. Импульс единичного кодового символа, пройдя со входа 11 через элемент запрета 4 на вход RS-триггера 3 управления, переводит

его в единичное состояние, при котором будут разрешены по первому входу элементы

И 7 управляемых ключей. Поскольку RSтриггеры 8 этих управляемых ключей на- ходятся в нулевом состоянии, то на выходах элементов ИЛИ-НЕ 9 присутствуют едийичные сигналы, которые также разрешают элементы И 7 по третьему входу. Первыи следующий во времени импульс одной из последовательностей с выхода делителя 2 частоты (в данйом случае последовательность с первого выхода) проходкт через элемент И соответствующего управляемого ключа и элемент ИЛИ 6 на выход устройства. Одновременно импульс с выхода элемента И устанавливает RS-триггер 8 этого же управляемого ключа в единичное состояние, при котором сигнал с выхода RS-триггера 8, пройдя через элемент ИЛИ-НЕ 9 соответствующего управляемого ключа, запрещает элемент И 7 этого, управляемого ключа по третьему входу. Таким образом, на выход устройства поступает импульсная ! последовательность с первого выхода делителя 2 частоты. Этот процесс продолжается до поступления на вход 10 устройства следующего импульса, соответствующего перед нему фронту единичного кодового символа, после чего аналогичным образом происходит выбор импульсной последовательности, имеющей в створе единичного кодового символа целый импульс, следующий после начала единичного символа. Если к мбменту окончания импульса на входе 10 устройства имеется импульс на одйом из выходов делителя 2 частоты, то RS-триггер 3 управления не может перейти в единичное состояние сигналом с выхода элемента запрета 4, так как на его запрещающий вход действует сигнал с выхода элемента ИЛИ 5. Переход RSтриггера 3 управления в единичное состояние происходит только после окончания импульса на первом выходе делителя 2 частоты и в дальнейшем устройство синхронизации функционирует как описано, т. е. на выход поступает импульсная последовательность, имеющая первый целый импульс внутри ство ра единичного кодового символа.

Формула изобретения

40 триггера, к S-входу которого подключен выход второго элемента И, а выходы первого и второго элементов И подключены ко входам зторого элемента ИЛИ, причем íà R-вхо45 ды RS-триггера управления, первого и второго дополнительных RS-триггеров и на соответствующий вход первого элемента ИЛИ подана последовательность импульсов, соответствующих передним фронтам кодовых символов входного сигнала, а на сигнальный

1s

ze и

36

Устройство для синхронизации дискретных сигналов, содержащее последовательно соединенные генератор импульсов и делитель частоты и последовательно соединенные

RS-триггер управления и первый элемент И, а также второй элемент И, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм, введены последовательно соединенные первый элемент ИЛИ и элемент запрета, а также второй элемент ИЛИ, два дополнительных RS-триггера и два элемента ИЛИ-НЕ, при этом выход элемента запрета подключен к S-входу RS-триггера управления, выход которого подключен к одному из входов второго элемента И, к двум другим входам которого подключены соответственно выход делителя частоты, о бъединенный с соответствующим входом первого э,лемента ИЛИ, и выход второго элемента ИЛИ-НЕ, ко входу которого подключен выход первого дополнительного RSтриггера, к S-входу которого подключен выход первого элемента И, к двум другим входам которого по,",ключены соответственно соответствующий выход делителя частоты, объединенный с соответствующим входом первого элемента ИЛИ, и выход первого элемента ИЛИ-НЕ, ко входу которого подключен выход второго дополнительного RSвход элемента запрета подан информационный сигнал.

Источники информации, принятые во внимание при экспертизе

1. Дудлн Г. К,. Схема на феррит-полу- проводниковых ячейках в аппаратуре связи.

М., «Связь», 1968, с. 284 (прототип).

720768

Составитель Г. Серова

Редактор О. Степина Техред К. Шуфрич Корректор Е. Папп

Заказ 10246/49 Тираж 729 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ПП П « Патент», г. Ужгород, ул. Проектная, 4