Устройство для приема многочастотных сигналов

Иллюстрации

Показать всеРеферат

v° . г, .д и па..е .нс те,:и, еокая. ..они еи Б

ИЗОВРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сеюз Сееетскии

Социалистических

Реслублик 720824 (61) Дополнительное к авт. свид-ву— (22) Заявлено 05.06.78 (21) 2631148/18-09 (51) М. Кл . с присоединением заявки №вЂ”

Н 04 Q 1/46

Ртерааратееииый кемитет

СССР ао делам изабретеиий и етирытий (23) Приоритет— (53) УДК 621.395..632 (088.8) Опубликовано 05.03.80. Бюллетень № 9

Дата опубликования описания 15.03.80 (72) Авторы изобретения

В. Ю. Толубеев и А. Г. Долинский (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОЧАСТОТНЫХ СИГНАЛОВ

Изобретение относится к технике связи и предназначено, в частности, для приема многочастотных сигналов, передаваемых токами тональных частот кодом «2 из п», è преобразования их в сигналы, пригодные для управления коммутационным оборудованием электронных и квазиэлектронных автоматических телефонных станций (АТС) .

Известно устройство для приема многочастотных сигналов, содержащее входной усилитель, выход которого соединен с и каналами, содержащими последовательно соединенные полосовой фильтр, пороговый элемент и интегратор, а также последовательно соединенные блок памяти и выходной вентиль (где и — число принимаемых частот) а также блок анализа кода, блок задержки, выходной блок памяти и выпрямительный блок, причем вход выпрямительного блока соединен с выходом входного усилителя, а выход выпрямительного блока подключен ко вторым входам пороговых элементов (11.

Однако помехоустойчивость такого устройства при приеме сигналов с частотным перекосом уровней невелика.

Цель изобретения — повышение помехоустойчивости устройства при приеме сигналов с частотным перекосом уровней.

Цель достигается тем, что в устройство для приема многочастотных сигналов, содержащее входной усилитель, выход которого соединен с п каналами, содержащими последовательно соединенные полосовой фильтр, пороговый элемент и интегратор, а также последовательно соединенные блок памяти и выходной вентиль (где n — число принимаемых частот), а также блок анализа кода, блок задержки, выходной блок памяти и выпрямительный блок, причем вход выпрямительного блока соединен с выходом входного усилителя, а выход выпрямительного блока подключен ко вторым входам пороговых элементов, введены формирователь опорного напряжения, а в каждый канал введен сумматор по модулю два, первый вход которого соединен с соответствующим входом блока анализа кода, с первым входом соответствующего блока памяти и с выходом интегратора, вторые входы блоков памяти соединены с выходом блока задержки и первым входом выходного блока памяти, втофайф *. .,:-.., —, м-. - . ° - " „ ",; . - -", -, . -ФЯмщ:-б-""- -.-- -";."7 .." =- —.— : - - - 3 ... - - . - 720824 рой вход которого соединен с выходом бло- Вйдеоимпульсы с выходов интеграторов ка айалйза кода, причем вторые выходы бло- .:. 5 поступают на вход сумматоров 6 по модублока "задержкй, йричем"вторйе=вХбдь| Ъй - > "ненй"и подключены ко входу блока 10 заходных вентилей Сждйненйю с BbIxîäîì вы- держки, то фройтом импульсов запускается ходного зайоминающего блока,— а выходы блок 10 задержки и- через калиброванный

* фо ФТроватЖя Опорйбго напряжения сое- промежуток времени информация с выхода

"Кйнень1 сб вторыми входами пороговых бло- блока 7 памяти поступит на входы выходных вентилей 8. ов. . "..

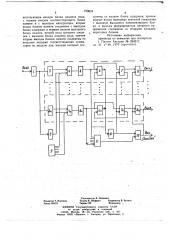

На чу еже показана структурная элек- 14 Ёсли информация поступает в заданном трическая схема устройства для йриема мно- коде, то на выходе блока 11 анализа кода го4аСтотйых сигналов. - " " — сигнал отсутствует и информационные сигСхема устройства "содержит входной уси- " налы проходят на выходы вентилей 8. литель 1, к выходу которого параллельно под- Если же блок 11 анализа кода опредеключены выпрямительный блок 2 и входы п 1 лит, что поступающая информация пере каналов, каждый йз" которых состойт из * "дается не"в заданном коде, то есть, пере- " оследовательно включенных IIQJIocoBol дается ток одной частоты или тоКи более, фильтра 3, порогового элемента 4; вфйм: "" ";чем двух частот,"то в этом случае на выхойенного на -Квухвходовом компараторе, ин- де блока 11 анализа кода появляется сиг тегратора 5, сумматора 6 по"мбд йЮ два, нал; который с выхода выходного блока 12 блока 7 памяти"и выходного вентиля 8 Вто- памяти подается на блокирование всех вы рйЕ вХоды пороговых- элементов 4 соеКй- " ходных вентилей 8. Одновременно этот сигненй с выходом выпрямительного блока 2 "- йал йоступает на--выходную клемму сигна="й с" соотвествующим выходом формирова- . ла «ошибка». теля 9 ойорного напряжения-;. -.:- — - - Так как вторые входы пороговых элеменПервый вход блока 7 памяти и первый 2 тов 4, кроме формирователя опорного навход сумматора 6 пб модулю-два"соедййены " йряжения, соединены также с выходом выс вЪ ходдм интегратора 5, а второй Вход прямительного блока 2, то при увеличениисумматора 6 подключен к второму выходу уровней входных сигналов (при коротких блока 7 памяти. Выходьгсумматоров 6 всех " соединительных линиях) увеличивается выду блока (0 задержки; выход которого сое- мительного блока 2, которое, поступая на

30 динен со вторыми входами блоков 7 ЙЙВгя- " ""вторые входы пороговых элементов 4 смещает порбги чувствительности в сторону

Выходы всех интеграторов 5 подключены их увеличения. Это позволяет сохранить к входам блока 11 аналйза- коКа," выход ко- постоянство рабочей полосы частот каждого

Ирбгб сОедйнеМ "с вторым входом выходно- gg канала устройства в широком динамичес-, го блока 12 памяти",, " . " ком диапазоне уровней входных сигналов.

Выход блока 12 ггамятй йо31ключей ко вторйМ" входам выходных вейтилеи 8 и од " " новремейно является ""вйходом сигнала Формула изобретения

«ошибка», а считывающий вход блока 12.

=Ъй гятй""соединен с выходом блока 10 за- Устройство для приема многочас1отных ." держки — " ", . "" " "" снгналов, содержащее входной усилитель, выход когорого соединен с и каналами, соУстройство работает следующим образом. " "дерЖащими последовательно соединенные

СиrNaYihi; "передаваемые токами двух полосовой фильтр, пороговый элемент и ин- = частот нз и, ннапрймер f> и „„усМйява|отся-ii erpатор, а также последовательно соеди входным усилителем 1 и через-" йблосовые ненные блок памяти и выходной вентиль фильтры 3 соответствующих каналов iio- (где п — число принимаемых частот), а

"" "даются на один -из входов порогового эле- также блок анализа кода, блок задержки, мента 4. На вторые входы" пороговых эле - выходной блок памяти и выпрямительный ментов 4 подайтся йЬЯВяййые"йапряжения блок; причем вход выпрямительного блока

50 смеШенйя"с соответствующих выходов фор- сбединен с вйходом входного усилителя, а мирователя 9 ойорйого =нйф3Ь ЙФййГ и тем выход выпрямительного блока подключен

Ж М"ЙИ устЖЫвлйвается разлйчйая чувстви- ко вторы " " тельй"осчь "к а н ал бв" itsf " ного йерекоса затухайия соединительных ли- помехоустойчивости при приеме - сигналов ний. С выхода порогового элемента 4 огра- л с частотным перекосом уровней, введены "ййчейнь1е re "амйлйтуде сигйалы поступают формирователь опорного напряжения, а в на"входы интегратора 5, где выделяются их каждый канал введен сумматор по модулю огибающие.""" - —:- два, первый вход которого соединен с соот720824 ветствующим входом блока анализа кода, с первым входом соответствующего блока памяти и с выходом интегратора, вторые

Ъ входы блоков памяти соединены с выходом блока задержки и первым входом выходного блока памяти, второй вход которого соединен с выходом блока анализа кода, причем вторые выходы блоков памяти соединены со вторыми входами соответствующих сумматоров по модулю два, выходы которых соеь динены со входом блока задержки, причем вторые входы выходных вентилей соединены с выходом выходного запоминающего блока, а выходы формирователя опорного напряжения соединены со вторыми входами пороговых блоков.

Источники информации, принятые во внимание при экспертизе

1. Патент Австрии № 284917, кл. 21 а 40, 1970 (прототип).

Составитель В. Лякишев

Редактор T. Портная Техред К. Шуфрич .: Корректор В. Бутяга

Заказ 350/23 Тираж 720 Подписное л --;=

ЦЙИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Рауигская наб., д. 4/5

Филиал ППП <Патент>, г. Ужгород, ул. Проектная, 4