Устройство для приема адресной комбинации

Иллюстрации

Показать всеРеферат

ОП ИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (1и72О826

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 13.07.78 (21) 2644067/18-09 с присоединением заявки №вЂ” (51) М. Кл2.

Н 04 Q 3/04

Гааударотееииый комитет

СССР до делам изобретений и открытий (23) Приоритет—

Опубликовано 05.03.80. Бюллетень № 9 (53) УДК 621.395.. 632 (088.8) Дата опубликования описания 16.03.80 в

Г. И. Азаров, Ю. Н. Манякин и Ф. М. Коробейников (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРИЕМААДРЕСНОЙ КОМБИНАЦИИ

Изобретение относится к технике связи и может использоваться в аппаратуре селективного вызова.

Известно устройство для приема адресной комбинации, содержащее преобразователь сигнала, последовательно соединенные опорный генератор и делитель частоты, а также дешифратор, выход которого подключен к первому входу блока сравнения (1).

Однако известное устройство для приема адресной комбинации обладает низкой помехоустойчивостью..

Цель изобретения — повышение помехоустойчивости.

Для этого в устройство для приема адресной комбинации, содержащее преобразователь сигнала, последовательно соединенные опорный генератор и делитель частоты, а также дешифратор, выход которого подключен к первому входу блока сравнения, введены формирователь импульса, два бистабильных элемента, инвертор и элемент

Шеффера, при этом выход преобразователя сигнала подключен к первому входу формирователя импульса, первый и второй выходы которого через соответствующие бистабильные элементы подключены ко входам элемента Шеффера, выход которого подключен к другому входу делителя частоты, первый выход которого подключен ко входу дешифратора, а второй выход подключен ко второму входу формирователя импульса и ко входу инвертора, выход которого подключен к другим входам бистабильных элементов, причем соответствующий выход формирователя импульса подключен ко второму входу блока сравнения.

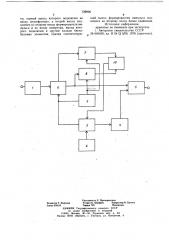

На чертеже приведена блок-схема устройства.

Блок-схема устройства для приема адресной комбинации содержит преобразователь 1 сигнала, опорный генератор 2, делитель 3 частоты, дешифратор 4, блок 5 сравнения, формирователь 6 импульса, два бистабильных элемента 7 и 8, инвертор 9 и элемент Шеффера 10.

Устройство работает следующим образом.

С выхода канала связи частотно-модулированные сигналы (частота заполнения единичныХ посылок fi, нулевых 1з) поступают на вход преобразователя 1 сигнала.

720826 и зо

Формула изобретения з

С выхода преобразователя 1 сигналы в виде последовательностей «1» и «О» поступают на информационный вход формирователя 6 импульса, основным элементом которого является, например, триггер Dt-типа.

Импульсы, поступающие на информационный вход формирователя 6, записываются в него только после ухода положительного тактового импульса. Следовательно, максимально возможная задержка продвижения информации, вызванная введением формирователя 6 импульса, равна периоду тактовых импульсов.

Для уменьшения времени задержки частота тактовых импульсов в устройстве выбирается максимально возможной (равной, например, частоте опорного генератора 2).

Таким образом, с помощью формирователя 6 импульса происходит восстановление искаженных фронтов исходных импульсов и обеспечивается их привязка к фрон— там тактовых импульсов.

С первого выхода формирователя 6 импульсы поступают на первый вход блока 5 сравнения, на другой вход которого подается импульсная последовательность с дешифратора 4, соответствующая адресу данного устройства. Тактовые импульсы для регистра дешифратора 4 формируются делителем 3 частоты.

Работа блока 5 сравнения и дешифратора 4 идентична работе аналогичных узлов известного устройства.

Для поддержания временных соотношений между передатчиком и приемником применяется синхронный способ. Устойчивость синхронизации в условиях флуктуаций обеспечивают бистабильные элементы 7, 8, инI вертор 9 и элемент Шеффера 10.

В качестве бистабильных элементов 7, 8 могут быть применены, например, RS-триггеры с инверсныМи входами.

Смена состояний на выходе формирователя 6 импульса возможна только в момент ухода положительных тактовых импульсов, т. е. в поСледующиЙ момент времени после записи в него информации уровень выходных импульсов будет нулевым. Для устранения состояния неопределенности на выходах бистабильных элементов ?, 8 необходимо исключить одновременное появление

«О» на обоих входах бистабильных элементов 7, 8. Это достигается с помощью инвертора 9, обеспечивающего единичное состояние на установочных входах бистабильных элементов 7, 8 при смене информации на их информационных входах.

Сигналы с выхода преобразователя 1 подаются на информационный вход формирователя 6 импульса и тактовым импульсом, поступающим с дополнительного выхода делителя 3 частоты, переписываются на выход. формирователя 6 импульса. Эти же сигналы соответственно будут и на информационных входах бистабильных элементов 7, 8.

На установочные входы бистабильных элементов 7, 8 подаются инвертированные инвертором 9 тактовые импульсы и обеспечивают наличие «1» на установочных входах бистабильных элементов 7, 8 в моменты смены уровней на их информационных входах.

С приходом «О» посылки на информационные входы бистабильных элементов 7, 8 на выходе второго бистабильного элемента 8 установится «1» состояние, а на выходе первого бистабильного элемента останется предыдущее состояние, так как бистабильный элемент 7 или 8 сохраняет свое состояние до прихода «О» на его установочный вход. !

Таким образом, в течение времени, равного длительности тактовых импульсов, на выходах обоих бистабильных элементов 7, 8 будет «1», а на выходе элемента Шеффера 10 — «0».

Аналогичная картина наблюдается по окончании «1» посылки, когда на выходе элемента Шеффера 10 также формируется импульс синхронизации. Отличие состоит лишь в том, что хранение информации происходит в этом случае вторым бистабильным элементом 8.

Импульсы синхронизации с выхода элемента Шеффера 10 поступают на синхронизирующий вход делителя 3 частоты и устанавливают его в исходное состояние. Таким образом производится подстройка фазы тактовых импульсов регистра дешифратора 4 при приеме адресной комбинации.

Использование предложенного устройст-, ва повышает помехоустойчивость приема адресных комбинаций в 1,5 — 1,7 раза.

Устройство для приема адресной комбинации, содержащее преобразователь сигнала, последовательно соединенные опорный генератор и делитель частоты, а также дешифратор, выход которого подключен к первому входу блока сравнения, отличающееся тем, что, с целью повышения помехоустойчивости, введены формирователь импульса, два бистабильных элемента, инвертор и элемент Шеффера, при этом вйход преобразователя сигнала подключен к первому входу формирователя импульса, первый и второй выходы которого через соответствующие бистабильные элементы подключены ко входам элемента Шеффера, выход которого подключен к другому входу делителя часто720826

Составитель Е. Прозоровская

Редактор Т. Портная Техред К. Шуфрич Корректор В. Бутяга

Заказ 350/23 Тираж 720 Подписное

ЦН И И ПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная. 4

5 ты, первый выход которого подключен ко входу дешифратора, а второй выход подключен ко второму входу формирователя импульса и ко входу инвертора, выход которого подключен к другим входам бистабильных элементов, причем соответствуюь

1ций выход формирователя импульса подключен ко второму входу блока сравнения.

Источники информации, : принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 640456, кл. Н 04 Q 5/00, 1976 (прототип).