Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

О Il Ц,,4",; 4 И И Е

ИЗОБРЕТЕН ИЯ

Союз Советскнк

Социалистических

Республик (1!) 721828

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено 27.09. 78 (21) 2667121/18-24 (53)M. Кл.

G 06 G 7/16 с присоединением заявки М— (23) Приоритет

>>>вуАвретве»вы% KoNHToT

СССР ав аевеи изобретений и втерытнв

ОпУбликовано 15.03.80. Бюллетень Ж 10

Дата опубликования описания 17.03.80 (53) УДК 681.335

{ 088.8) (72) Авторы изобретения

Н. И. Корсунов, Е. В. Корсунова и В. Н. Кондрятюк

Харьковский ордена Ленина политехнический институт им. В. И. Ленина (71) Заявитель (54) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в аналоговых вычислительных машинах, в устройствах автоматики и измерительной техники и в ряде других уст ройств, в которых необходимо проводить одновременно операции умножения и деления входных сигналов.

Известны устройства для одновременно

ro выполнения операций умножения и де»> пения, содержашие широтно-импульсный и амплитудный модулятор (lj. Эти устройства наряду с высокой стабильностью характеристик и технологичностью имеют ряд недостатков, к числу которых следу15 ет отнести требование гальванической развязки цепей широтно-импульсного M амплитудного модуляторов и повышенное потребление мошности от источника сигнала сомножителя, подключенного ко axogy амплитудного модулятора, Н аиболе е близким тех нич еск им решениЕм является устройство для умножения (2 J, содержяшее источники сигналов сомножителей, компаратор, интегратор и фазочувствительный выпрямитель, входы которого соединены с выходами интегратора и компаряторя, входы которого соединены с его выходом и с выходами интегратора и источника сигнала одного из сомножителей, а выходы интегратора подключены к выходам компаратора источника сигнала второго сомножителя.

Это устройство позволяет получить произведение сигнала или частное от деления при включении множительного устройства в обратную связь операционного усилителя, но не позволяет одновременно выполнять операции умножения и деления, что ограничивает его функциональные возможности и область применения.

Белью изобретения является расширение функциональных возможностей за счет одновременного выполнения операции умножения и деления.

Поставленная цель достигается тем> что в устройство, сопержяшее источники

V,=(u+ K„X)/ñ, /,=С-О+ К Ц/с.

3 7218 сигналов сомножителей, интегратор, вход которого подключен к одному из источников иигналов сомножителей, компаратор, входы которого подключены к выходам интегратора и источника сигнала другого сомножите5 ля соответственно, фазочувствительный выпрямитель, входы которого соединены с выходами интегратора и компаратора, дополнительно введены источник сигнала делителя и ключи, коммутируемые входы которых под-ip ключ ены соответственно к положительному и отрицательному выходам источникам сигнала делителя, а выходы ключей подключены ко входам интегратора и компаратора,а управляющие входы ключей подключены к 1Б выходу компаратора.

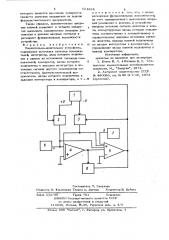

Блок-схема предлагаемого устройства приведена на чертеже, Устройство содержит двухполярный ис.— точник сигнала делителя 1, ключи 2 и 3, 20 интегратор 4, компаратор 5, источник сигнала сомножителя 6, источник сигнала сомножителя 7, фазочувствительный выпрямитель 8.

Устройство работает следующим об- 5 разом.

При сигнале делителя U не равном

О и отсутствии сигналов сомножителей

Х и Ч или ревенства одного из них, например, V О, компартор находится в ЗО одном из двух устойчивых состояний которым открывается один из ключей, а дру. гой закрывается. Для определенности примем, что ко входу ключа 2 подсоединен положительный выход источника сигнала Ç5 делителя 1, а кпюч 3 открывается отрицательными напряжениями на выходе компаратора 5. Если выходное напряжение компаратора 5 равно — 0к, то открытое состояние ключа 3 не приводит к изменению 4О состояния ..компаратора 5.

Под действием напряжения источника сигнала делителя 1 равного — u напря1

45 жение на выходе интегратора 4 линейно возрастает со скоростью Ч = —.. до велио чины порога срабатывания компаратора 5, равной U, при достижении которой компаратор 5 из состояния — 0к переходит в состояние + Ок . При переключении компа$Q ратора 5 ключ 3 закрывается и открывается ключ 2, что приводит к ускорению переключения компаратора 5 за счет положительного напряжения источника сигна55 ла делителя 1, подключенного ко входу ко (паратора 5, Переключение компаратора 5 приводит к изменению знака выходного напряжения фаэочувствительного вы28 4 прямителя 8. Напряжение на выходе интегратора 4 теперь линейно падает до величины — 0 при достижении которой комФ пара тор 5 вновь переключается.

Среднее значение выходного напряжения фазочувствительного выпрямителя 8, . которое може т бвть вы де лен о филь тром любой конструкции, равно нулю.

При неравенстве нулю сигналов сомножителей и положительном напряжении на выходе компаратора 5 в открытом состоянии находится ключ 2 и скорость интегрирования определяется из выражения а при отрицательном напряжении на выходе компаратора 5 и открытом ключе 3 скорость интегрирования

Если при положительном выходном напряжении компаратора 5 на его выход подан положительный сигнал от источника второго сомножителя, то порог срабатывания компаратора 5 равен

0 =О+К„ / а при отрицательном напряжении на выходе компаратора 5 порог срабатывания

U)=-V+K„Y, Длительность положительного импульса на выходе компаратора 5 определяется выражением

4 =(0 0)V =2О /С0 К Х)

2 Я 4 2. х а длительность отрицательного импульса

,=Со;О,)/Ч„=г. О И0-К„М, Период напряжения на выходе компаратора 5 и соответственно на выходе устройства равен т = =a u /со -к х ), 2. х

Среднее значение выходного напряжения устройства определяется выражением

0 (х X (0++ Y)

40 t 2(0-К„Х)

Е(о К„Ч> (:(U-K„Y) с(-О К„ЧР

2(и-K„X) 2(U+K Х> 2(U K„X>

=К К XY/О

ИзмЕнение полярности напряжения источника сигнала делителя приведет к зеркальному отображению эпюр выходных на пряжений узлов устройства, следствием

7218 которого является изменение полярности среднего значения напряжения на выходе фазочувствительного выпрямителя, Таким образом, дополнительное введение ключей позволяет в четырех квадратах выполнить одновременно операцию умножения и деления входных сигналов и расширяет функциональные возможности устройства.

Формула изобретения ip

Множительно-делительное устройство, содержашее источники сигналов сомножителей, интегратор, вход которого подключен к одному иэ источников сигналов сомножителей, компаратор, входы которого f5 подключены к выходам интегратора и источника сигнала другого сомножителя соответственно, фазочувствительный Выпрямитель, входы которого подключены к выходам интегратора и компаратора, о т — 20

28 6 л и ч а ю ш е е с я тем, что, с целью расш ирен ия функциональных возможностей, за счет одновременного выполнения операций умножения и деления, в устройство введены источник сигнала делителя и ключи, коммутируемые входы которых подключены соответственно к положительному и отрицательному выходам источника сигнала делителя, выходы ключей подключены ко входам интегратора и компаратора, а управляюшие входы ключей подключены к выходу компаратора.

Источники информации принятые во внимание при экспертизе

1. Бенин В. Л. и Кизилов В. У. Статические измерительные преобразователи мошности, М., "Энергия, 1972.

2. Авторское свидетельство СССР

Ж 480086, кл. G 06 G 7/16, 1973 (прототип).

Составитель Т. Сапунова

Редактор Н. Каменская Texpen Q, Легеэа Корректор В. Бутяга

Заказ 132/40 Тираж 751 Подписное

IlHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4