Вычислительное устройство

Иллюстрации

Показать всеРеферат

Союз Советскик

Социапистическил

Ресттублик

ОП ИСАНИ

ИЗОБРЕТЕН И

К АВТОРСКОМУ СВИДЕТЕЛЬСТВ (61) Дополнительное к авт. свид-ву (22) Заявлено 27.09.78 (21) 2667152 18 с присоединением заявки РЙ— (23) Приоритет

Опубликовано 15.03.80. Бюллетень J%

Дата опубликования описания 18.03

М. Кл.

6 G 7/16. Ваударственный кемнтет

СССР до делам нэебретеннй н еткрытнй

Д К68 1.33 5 (088.8) (72) Автор. изобретения

H. И. Корсунов

Харьковский ордена Ленина политехнический институт им. B. И. Ленина (7l ) Зачвитель (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРО ЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в аналоговых вычислительных машинах, устройствах автоматики и измерительной техники, а также в ряде других устройств, в которых необходимо прово5 дить одновременно операции умножения и деления, Известны устройства для одновременного выполнения операций умножения и деления, содержашие широтно-импульсный и амплитудный модулятор pl).

Однако эти устройства имеют сушественные недостатки: при работе требуется введение гальванической развязки между цепями широтно-импульсного и амплитудных модуляторов и повышечная мошность потребления от источника сигнала сомножителя, подключенного ко входу амплитудного модулятора. 26

Наиболее близким техническим решением является устройство для умножения (2, содержашее источники сигналов сомножителей; компаратор, интегратор и фазочувствительный выпрямитель, входы которого подключены к выходам интегратора и компаратора, входы компаратора rtopключены к выходам интегратора и источника сигнала одного из сомножителей, а

/ выход источника сигнала другого сомножителя подключен ко входу интегратора.

Это устройство позволяет получать раздельно произведение входных сигналов и частное от деления при включении его в обратную связь операционного усилителя, но не позволяет одновременно выполнять операции умножения и деления. Это ограничивает его функциональные возможности и сужает область применения.

Целью изобретения является расширение функциональных воэможностей устройства за счет одновременного выполнения операций умножения и деления. . Поставленная цель достигается тем, что в устройство, содержашее источники сигналов сомножителей, интегратор, компаратор, вход которого подключен к источнику сит.нала одного из сомножителей

v,= — с0 к X), V = -0+Ê X), 1

2, C х

1 р т с(-И. К„Ч) х

Я. -U +К„Y)

2(0+К у) х 0

)(Y

3 72 182 и к выходу интегратора, ко входу интегратора подключен источник сигнала другого сомножителя, и фазочувствительный выпрямитель, входы которого подключены соответственно к выходам интегратора и компаратора, дополнительно введены источник сигнала делителя и ключи, коммутируемые входы которых подключены K соответствуюшим . выходам источника сигнала делителя, выходы ключей подключены ко входу интегратора, а управляюшие входы ключей подключены к выходу компа ра тора.

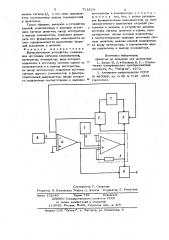

Схема предлагаемого устройства приведена на чертеже. 15

Устройство содержит двухполярный источник сигнала делителя 1, ключи 2 и 3, интегратор 4, компаратор 5, источник сигнала сомножителя 6, источник сигнала сомножителя 7, фазочувствительный ро выпрямитель 8, Устройство работает следуюшим образом.

При отличном от нуля сигнале делителя на выходе источника 1 и равенстве нулю 25 одного или обоих сигналов сомножителей на выходах источников 6 и 7, компаратор

5 находится в одном из двух устойчивых состояний, например - 0 Это приводит к открытию одного из ключей, напри- ЗО мер ключа 2, и запиранию второго. 8 зависимости от полярности сигнала Ц, подаваемого от источника сигнала делителя ко входу ключа 2, напряжение на выходе интегратора 4 линейно возрастает или ли- зБ

О нейно убывает со скоростью Ч=- — (где — постоянная времени интегратора).

Для определенности примем, что напряжение на выходе интегратора 4 возрастает и повторяется на выходе фазочувствитель- 40 ного выпрямителя 8. Когда выходное напряжение интегратора 4 достигает порога срабатывания компаратора 5 +Ц, послед- ний регенеративно переходит в состояние

+0 Это приводит к тому, что напря- 45 жение на выходе интегратора линейно убывает и повторяется с противоположным знаком на выходе фазочувствительного выпрямителя 8. При достижении выходным напряжением интегратора 4 величины $Q

0р компаратор 5 вновь переключается, и процесс повторяется, Среднее значение напряжения на выходе фаэочувствительного выпрямителя, которое может быть выделено фильтром любой конструкции, равно нулю.

При наличии сомножителя )(на выходе источника сигнала 6, подаваемого на

9 4 вход интегратора, и положительном напряжении на выходе компаратора 5, открывается ключ 3 и скорость интегрирования определяется выражением а при отрицательном напряжении на выходе компаратора 5 скорость интегрирования

Если при атом на вход компаратора 5 подан сигнал+ у от источника сигнала сомножителя 7, то порог срабатывания компаратора 5 при положительном напряжении на его выходе равен и при отрицательном напряжении на выходе компаратора, порог срабатывания

Длительность положительного импульса на выходе компараторов 5 определяется выражением

U-0 20 с

7; UК„Х а длительность отрицательного импульса

Период напряжения на вйходе компаратор 5 и соответственно на выходе устройства равен

40 0 T=t +f. = — - -у0-К X х

Среднее значение выходного напряжения на выходе фазочувствительного выпрямителя о -к х <и к y>

0ььх. 40 0 С 2(0-К„Х) о Ъ (ОЧ „Х7

Следовательно, выходное напряжение устройства пропорционально произведению сигналов Х и Y. и обратно пропорцио721829 нально сигналу Ц, и его знак определяется соотношением знаков сомножителей и делителем.

Таким образом, введение в устройство ключей, подключенных к выходам источника сигнала делителя, входу интегратора и выходу компаратора, позволяет расширить его функциональные воэможности эа счет одновременности выполнения операций умножения и деления.

Формула изобретения

Вычислительное устройство, содержащее источники сигналов сомножителей, интегратор, компаратор, вход которого подключен к источнику сигнала одного из сомножителей и к выходу интегратора, ко входу интегратора подключен источник сигнала другого сомножителя, и фазочувствительный выпрямитель, входы которс го подключены соответственно к выходам

6 интегратора и компаратора,. о т л и ч а— ю ш е е с я тем, что, с целью расширения функциональных возможностей, за счет одновременного выполнения операций умножения и деления, в устройство введены источник сигнала делителя и ключи, коммутируемые входы которых подключены к соответствующим выходам источника сигнала делителя, выходы ключей подключены

10 ко входу интегратора, а управляющие вхрды подключенЫ к выходу компаратора.

Источники информации, принятые во внимание при экспертизе

1. Бенин В. Л.и Кизилов В.У, ° Статические измерительные преобразователи мощности М., "Энергия, 1972.

2. Авторское свидетельство СССР

М 480086, кл. G 06 G 7/16, 1973 (прототип) .

Составитель Г. Сапунова

Редактор Н. Каменская Техред O. Дегеза Корректор Г. Решетник

Заказ 132/40 Тираж 751 Подписное

UHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4