Многоразрядное множительное устройство

Иллюстрации

Показать всеРеферат

.; b3(cC

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советскик

Социалнстическик

Республик (iii721837

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву— (22) Заявлено05. 12.77 (21}2549993/18-24 с присоединением заявки,% (51 } М. Кл.

506 3 3/00

Веударствеяьй камитет

СССР во деяам изобретений н открытия (23) ПриоритетОпубликовано 15.03.80. Бюллетень .% 10

Дата опубликования описания 17.03.80 (53) УДК 681.335. ,8 (088.8) (72) Авторы изобретения

Ю. А. Кочкарев и В. П. Ратушняк

Таганрогский радиотехнический институт им. В. Д. Калмыкова (7I ) Заявитель (54) МНОГОРАЗРЯДНОЕ МНОЖИТЕЛЬНОЕ

УСТРОЙСТВО

Изобретение относится к аналоговой и гибридной вычислительной технике и предназначено для перемножения текущих значений многоразрядных чисел X и, Известно многоразрядное множительное устройство 1 с ортогональным кодированием информации, содержащее матрицу резисторов, управляемые ключи и операционный: усилитель, выход которого соединен с блоком нормализации.

Недостатком такого устройства является сложность структурной схемы и большое количество элементов.

Наиболее близким техническим решением к данному изобретению является

15 многоразрядное множительное устройство

P), содержащее генератор ортогональных сигналов и операционный усилитель с первым масштабным резистором в цепи обратной связи, выход операционного усилителя соединен со входом блока нормализации, первый выход которого является выходом устройства, а второй выход через второй масштабный резистор обратной связи соединен со входом операционного усилителя, к которому через соответствующие входные масштабные резисторы подключены выходы управляемых ключей первой группы.

Недостатком такого устройства является большое количество элементов и сложность структурной схемы, Целью изобретения является упрощение устройства.

Для этого предлагаемое многоразрядное множительное устройство содержит триггеры, вторую группу управляемых ключей и регистр, группа разрядных входов которого является первой группой разрядных входов устройства, а его выходы соединены с первыми входами управляемых ключей первой группы, вторые входы которых соединены с выходами соответствующих триггеров, первые входы управляемых ключей второй группы являются второй группой разрядных входов устройства, а их вторые входы соединены с выходом генератора ортогональных сигналов, к которому подключены

3 72 183 также управляющий вход регистра и первые входы триггеров, второй вход каждого из которых соединен с выходом соответствующего управляемого ключа второй гру пп ы.

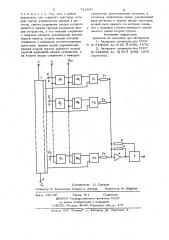

На чертеже представлена структурная схема предлагаемого устройства.

Многоразрядное множительное устройсвто. содержит регистр 1, группа разрядных входов которого является первой 10 группой разряднь|х входов устройства.

К выходам регистра 1 подключены первые входы управляемых ключей 2 — 2и, выполненных, например, на логических элементах И, к выходам которых подключены входные масштабные резисторы

3, — 3 . Резисторы 3 подключены ко входу операционного усилителя 4 с масштабным резистором 5 в цепи обратной связи. К выходу усилителя 4 подключен блок нормализации 7, один из выходов которого является выходом всего устройства, другой выход подключен через второй масштабный резистор 6 ко входу усилителя 4. Устройство также содержит вторую группу управляемых ключей 8 - 8, выполненных на элементах И. Один из входов каждого элемента И 8 подключен к выходу генератора ортогональных сигналов 9, и которому подключены также управляющий вход регистра 1 и входы триггеров 10 4 — 10 .

Устройство работает следующим образом.

Н а соответствующие входы ус тройс тв а поступают сигналы, несущие информацию о многоразрядных сомножителях и в виде несинусоидальных сигналов, ортогональные составляющие которых в двоичной системе счисления пропорцио нальны величинам соответствующих раэ рядов чисел к и J . .Таким образом, величины Х и "представлены в ортогональной системе кодирования, причем в качестве ортогонального базиса приня- 4 ты функции Хаара одинакового ранга, взятые по абсолютной величине. Регистр 1 управляется генератором ортогональных сигналов 9 тактовой частотой % причем длительность такта должна быть равна длине интервала времени, на котором функции Хаара, принятые для кодирования информации, отличны от нуля.

Сомножитель g записывается в триггерах 10, начиная с младшего разряда.

Разрядная запись обеспечивается подачей иа ВхОды управляемых ключсй 8 ортого иальных составляющих 3," от геперато7 4 ра ортогональных сигйалов 9. При этом линейка резисторов 3, — З„оказывается набрана таким образом, что представляет собой двоичный код многоразрядного числа, т.е. если < -ый разряд многоразрядного числа Ч равен единице, то

-ый по счету сверху резистор 3 вкгючается между выходом регистра 1 и входом сумматора 4 через управляемый ключ 2. Если же 1 -ый разряд равен нулю ($ О), то указанный резистор не включается.

На каждом такте на выходе усилителя

4, если не принимать во внимание дейст вие блока нормализации, вырабатывается сигнал, пропорциональный соответствующему разряду результата вычислений в ненормализованной форме. Нормализация результата осуществляется в блоке нормализации 7, который имеет два выхода. Один выход блока 7, на котором вырабатываются нормализованные сигналы, является выходом всего устройства, а второй выход, на котором вырабатывается сдвинутый на один такт сигнал переноса, подключен через масштабный резистор 6 ко входу операционного усилителя 4. Следовательно, при выработке очередного разряда усилитель 4 на каждом такте одновременно учитывает и величину сигнала переноса из младшего разряда.

Сигналом 5 триггеры 10 сбрасываются в исходйое состояние, а на поси Н ледний разряд регистра записывается О, в результате чего схема переводится в исходное состояние.

Положительный эффект заключается в уменьшении количества элементов многоразрядного множительного устройства.

Формула изобретения

Многоразрядное множительное устройство, содержащее генератор ортогональных сигналов и операционный усилитель с первым масштабным разистором в цепи обратной связи, выход операционного усилителя соединен со входом блока нормализации, первый выход которого являет-ся выходом устройства, а второй выход через второй, масштабный резистор обратной связи соединен со входом операционного усилителя, к которому через соответствующие входные масштабные резисторы подключены выходы управляемых ключей первой группы, о т л и—

1837

y "2 s т Составитель О. Сахаров

Редактор Н. Каменская Техред О. Легеза Корректор М, Шароши

Заказ 132/40 Тираж 75 1 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и. открытий

113035, Москва, Ж-35, Раушская наб.,д., 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проетная, 4 ч а ю ш е е с я тем, что, с целью упрошения, оно содержит триггеры, вторую группу управляемых ключей и регистр, группа разрядных входов которого является первой группой разрядных входов устройства, а его выходы соединены с первыми входами управляемых ключей первой группы, вторые входы которых соединены с выходами соответствуюших триггеров, первые входы управляемых ключей второй группы являются второй группой разрядных входов устройства, а их вторые входы соединены с выходом

6 генератора ортогональных сигналов, к которому подключен ы также уп р авляюший вход регистра и первые входы триггеров, второй вход каждого из которых соединен с выходом соответствуюшего управляемого ключа второй группы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

10 N 516064, кл. G 06 У 3/00, 1976.

2. Авторское свидетельство СССР

No 524203, кл. ф 06 7 3/00, 1976 (прототип) .