Усилитель считывания на мдп-транзисторах

Иллюстрации

Показать всеРеферат

О П И,"С ";,"И И Е

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических

Республик (i 721852

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 02 10.78(21)2668819/18-24 с присоединением заявкк М (23) Приоритет

Опубликовано 15.03.80 Бюллетень Рй 10

Дата опубликования описания 20.03.80 (51)М. Кл.

G ll С- 11/34

Ртеудеретеенный кемнтет

СССР ае аелем нэебретеннй и еткрмтна (53) УДК 681.3 (088.8) (72) Авторы изобретения

С. А. Еремин, А. И. Стоянов, В. С. Хорошунов н В. А.Сухоруков (71) Заявитель (54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ

НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к вычислительной технике и может применяться в .МПД-запоминаюших устройствах с прон вольной выборкой информации: динамического типа для усиления сигналов нрн считывании и восстановления информации.

Известны усилители считывания - регенерации, применяемых в МДП-ЗУПВ, динамического типа 1Ц3 .

1 те

Обшнм недостатком известных уснлителей является низкая чувствительность, что приводит к малой надежности усилители. иель изобретения состоит в повыше ннн надежности устройства, Поставленная цель достигается тем, что усилитель счнтыванн .регенерации на МДП -транзисторах, содержашнй два переключаюших транзистора, истоки кото- Е рых соединены с шиной нулевого потенциала, сток первого переключаюшего тран. истора подключен х ввххоодду-выходу уснлнтеля и х затвору второго переключаю.шего транзистора, а сток второго - к затвору первбго, два нагрузочных транзнстора, стоки которых подключены к ши не питания, ттеток первого нагруэочного транзистора соединен со стоком первого переключаюшего транзисторар исток второго — со стоком второго нагрузочного транзистора, балансный транзистор, исток которого соединен с затвором одного нэ переключаюших транзисторов, стокс затвором другого, а затвор- с шиной управления, введены дополнительный транзистор, управляемый конденсатор н две дополннтел ьные шины уп равлення, исток допол ннтельного транзистора соединен с затвором конденсатора и с затвором первого нагрузочного транэнстора, сток - с входом-выходом усилителя, второй вывод управляемого конденсатора соединен с затвором второго нагрузочного транзистора, а затвор дополнительного транзистора н второй

I вывод управляемого конденсатора подключены к соответствуюшим дополнительным шинам управления.

721852 4 плеч триггера. После окончания действия импульса на шине ф транзистор 6 закры1 вается и "отсекает конденсатор 11 от большой емкости разрядной линии, подключенной ко входу-выходу усилителя. С приходом тактового импульса на шину ф э формируется окончательное состояние

1 триггера и производится регенерация информации в ячейке, Если конденсатор

10 11 имеет большую емкость в момент импульса на шине Ф, то на затворе з транзистора 5 формируется высокий уровень напряжения, и на входе-выходе усилителя возбуждается уровень логической

1, который записывается в ячейку, т.е, восстанавливает информацию в ячейн- ке, Если же конденсатор 11 в момент . включения Ф имеет малую емкость, то транзистор 5 остается в закрытом состоянии, и в ячейку записывается уро1 вень логического "0" °

Порог чувствительности усилителя определяется крутизной характеристики конденсатора и может достигать нескольких единиц милливольт.

Усилитель считывания на МДП-транзисторах, содержаший два переключаюших транзистора, истоки которых соединены с шиной нулевого потенциала, сток первого переключаюшего транзистора подключен к входу-выходу усилителя и к затвору второго переключаюшего транзистора, а

Сток второго - к затвору первого, два нагрузочных транзистора, стоки которых подключены к шине питания, исток первого нагрузочного транзистора соединен со стоком первого переключаюшего транзистора, исток второго-со стоком второго нагрузочного транзистора, балансный транзистор, исток которого соединен с затвором одного из переключающих транзисторов, сток - с затвором другого, а затворс шиной управления, о т л и ч а ю ш и йс я тем, что, с целью повышения надежности устройства, оно содержит дополнительный транзистор, управляемый конденсатор и две дополнительные шины управления, причем исток дополнительного транзистора соединен с затвором управляемого конденсатора и с затвором первого нагрузочного транзистора, сток - со входом-выходом усилителя, второй вывод

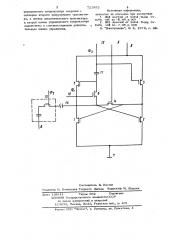

На чертеже показан предлагаемый уси л ител ь с чит ыван и я.

Ус ил ител ь содержит пере клю чаю шие

МДГ1-транзисторы 1 H 2 B триггерном соединении, причем затвор транзистора 1 соединен со стоком транзистора 2, с истоком нагрузочного транзистора 3 и с стоком балансного транзистора 4. Затвор транзистора 2 соединен со стоком транзистора 1, с истоком балансного транзистора 4, с истоком нагрузочного транзистора 5, со стоком дополнительного транзистора 6. Истоки переключаюших транзисторов 1 и 2 подключены к шине нулевого потенциала 7. Стоки нагрузочных транзисторов 3 и 5 соединены с шиной питания 8. Затвор балансного тра зистора 4 подсоединен с шине выбора кристалла 9, Затвор дополнительного транзистора 6 подключен к первой шине тактовых сигналов 10, а исток его— к затвору управляемого конденсатора 1 и к затвору нагрузочного транзистора 5.

Второй вывод конденсатора 11 присоединен ко второй шине Tàêòîâûõ сигналов

12 и к затвору нагрузочного транзистора 3. Ячейка памяти 13 соединена со входом-выходом усилителя 14.

В цикле предварительного заряда открывается транзистор 4, и в плечах Ф о р м у л а и э о б р е т е н и я триггера устанавливаются одинаковые уровни напряжения, близкие к пороговому (пороговые напряжения транзисторов и конденсатора равны). Так транзистор

6 открыт в цикле предварительного заряда, на затворе конденсатора 11 устанавливается пороговое напряжение, и режим его работы соответствует промежуточному между режимами "малой и "большой

40 емкости.

По окончании цикла предварительного заряда на шину Ф подается импульс, ко2 торый открывает адресный транзистор ячейки памяти, и на вход-выход усилите45 ля поступает приращение напряжения, знак которого определяется величиной уровня напряжения, записанного в ячейке, Если в ячейке хранится высокий. уровень напряжения то на входе - выходе усилителя ю

Ы формируется положительное прирашение напряжения которое переводит конденсатор

11 в режим "большой" емкости: если же в ячейке хранится низкий уровень напряжения, то приращение напряжений имеет отрицательный знак и конденсатор 11 пере водится в режим "малой емкости, Приращение напряжения на вход -выходе усилителя вызь вает небольшой разбаланс

721852 управляемого конденсатора соединен с затвором второго нагрузочного транзистора„а затвор дополнительного транзистора и второй вывод управляемого конденсатора подключены к соответствуюшим дополнительным шинам управления.

Источники информации, принятые во внимание при экспертизе

lEEE Зом iсй of Solid — State Circuits, voP. sc - б, N5, р. ЗО7

2. 1EEE Jour nal оЕ 5о@с% — State Circuits, vol. sc 7, й5, р. 338

3. Электроника, ¹ 4, 1976, с. 48.

Составитель В. Костин

Редактор H. Каменская ТехредО. Легеза Корректор М. Шароши

За ка з 1 38/4 1 Тираж 662 . Подписное

Ш1ИИГ1И Государственного комяететаСССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4