Устройство для контроля оперативной памяти

Иллюстрации

Показать всеРеферат

О Il И С А-""- --И- ЕИЗОБРЕТЕ Н ИЯ теi,н

Союз Советскнк

Социвпнстнческнз

Республик в 721853

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву (22) Заявлено 02.10,78 (21) 2668810/18-24 с присоединением заявки,йв (23) Приоритет

Опубликовано 15.03.80. Бюллетень М 10 (51)M. Кл.

11 . 29/00

1йеударетвенный квинтет

СССР ав лелем нзевретеннй н юткрмтнй (53) УДК 681,327 (088.8) Дата опубликования описания 20.03.80 (72) Авторы изобретения

Л. Ф. Салямов, И. К. Шопен и P. М. Колясникова (7l ) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВНОЙ

ПАМЯ ТИ

Изобретение относится к области зе» поминающих устройств и может быть использованодля контроля кубов памяти, накопителей, запоминающих устройств (ЗУ) автономно и в составе цифровых вычислительных машин.

Известно устройство для контроля оперативной памяти, содержащее, кроме обычных блоков вычислительных устройств, триггер со счетным входом, - включенный: тО например, между разрядными входом и выходом ЗУ. Правильность функциониро вания разряда контролируется на выходе

ЗУ с помощью осциллографа по характеуному мельканию выходных импульсов 1 .

$$

Недостатком этого устройства являет» ся невысокая полнота контроля.

Наиболее близким техническим реше нием к данному изобретению является устройство для контроля оперативной памяти, содержащее последовательно соеди» ненный генератор тактовых импульсов и счетчики, дешифраторы, схему сравнения, элементы И и ИЛИ, первый триггер, пртьчем одни из выходов первого и второго счетчиков подключены соответственно ко входам первого и второго дешифраторов, другие выходы первого и второго счетчиков и выход третьего счетчика соединены со входами элементов И, выходы которых подключены ко входам элемента ИЛИ„ вход первого триггера соединен с выходом элемента ИЛИ, а выходы подключены к одним из выходов устройства, входы схемы сравнения соединены соответственно с одним из выходов первого триггера входом устройства 21.

Недостатком этого устройства являет» ся отсутствие проверки сохранности инфор мации в контролируемом адресе при много» кратном обращении к соседним с ним адре»

c&M что необходимо для ЗУ, элементы памяти которых имеют общую среду. Этот недостаток снижает полноту контроля па»мяти.

11елью изобретения является увеличение полноты контроля.

721853

Поста вл е нна я цел ь дос тига етс я тем, что предлагаемое устройство содержит до« полнительные элементы И и ИЛИ, второй триггер и элемент НЕ, причем входы одного из дополнительных элементов И подключены соответственно к выходам генератора тактовых импульсов и элементов НЕ, а выход соединен со входом второго триггера, вход элемента HE подключен к выходу элемента ИЛИ, входы дополнительных элементов ИЛИ соединены с выходами второго дешифратора, первые входы других дополнительных элементов И подключены к выходам второго триггера, вторые входы - к выходам дополнительных элементов ИЛИ, а выходы - к дру гим выходам устройства.

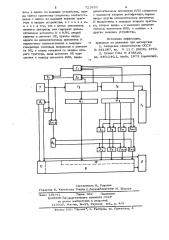

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит счетчики 1, 1

2 и 1, элементы И 2„и 2, элемейт

ИЛИ Э, дешифраторы 4 и 4 „, схему

С сравнения 5. Входы и выходы устройства, подключаются соответственно к выхо дам контролируемого ЗУ 6. Устройство также содержит генератор тактовых импульсов 7, первый 8 и второй 8, триггер, элемент НЕ 9, дополнительные элементы И 2 -2, и дополнительные элементы ИЛИ 3 -3 „„,, где o — целое число, ключи координатных шин 10 и ключи записи 11.

Входы элемента . И 2,, подключены соответственно к выходам генератора

7 и элемента НЕ 9, а выход соединен со входом триггера 8. Вход элемента

НЕ 9 подключен к выходу элемента ИЛИ

3, Входы элемента ИЛИ 3 — З,,„соединены с выходами дешифратора 4

Первые входы элементов И 2 — 2 под3 Tl+2 ключены к выходам триггера 8, вторые входы - к выходам элементов ИЛИ

3 - 3, а выходы - к выходам уст2 П+1 ройства.

Устройство работает следующим образом.

Тактовые импульсы генератора 7 изменяют состояние счетчика 1, а затем - счетчика 1 . Дешифраторы

4, и 4 управляют включением координатных шин 10 ЗУ через элементы

ИЛИ 3„-3,„и И 2 - 2„+ .. Далее происходит последовательный перебор шин

Х и выбор адресов зигзагом по двум соседним координатным шинам У, Г!ри обегании всех значений счетчика l g выбирается одна половина адресов ЗУ, расположенная относительно другой в

45

$0

5

25 шахматном порядке. От начального поло жения, триггера 8, управляющего включением координатных ключей 10 через элементы И 2., - 2„, зависит какая из половин адресов ЗУ будет выбираться при заполнении счетчиков 1 и 1 а э задержка переключения триггера 8 по счетному входу на один такт позволяет перейти на обращение к адресам другой половины С помощю двух многовходо вых элементов И 2, 2 . с выходов

Ф р счетчиков 1, 1 и 1 выделяются

2 3 два состояния: первое, когда они все обнулены, и второе - когда счетчики 1 и 1„ заполнены, а 1„ - обнулен. После обнуления счетчиков и дальнейшего поступления тактовых импульсов в одну группу адресов записывается некоторая информация, и последняя запись будет многократно повторяться по зигзагам и циклично до заполнения счетчика 1„

Схема сравнения 5 вырабатывает эталонные сигналы, аналогичные поступающим на усилители записи ЗУ 6 и включается после первого обращения ко всем адресам

ЗУ 6 (на втором цикле теста). Сигналы с выходов ЗУ 6 сравниваются с эталонными.

Предлагаемое устройство при миниму» ме -электронного оборудования позволяет увеличить полноту контроля ЗУ, а следовательно, надежность готовых изделий, включающих ЗУ. Особенно эффективно устройство для контроля ЗУ, элементы памяти которых имеют общую запоминающую среду, например ЗУ, содержащих магнитные дешифраторы на пластинах с равномерными отверстиями, работающими по принципу полувыборки со смешением.

Формула изобретения

Устройство для контроля оперативной памяти, содержащее последовательно соединенные генератор тактовых импульсов и счетчики, дешифраторы, схему сравнения, элементы И и ИЛИ, первый триггер, причем одни из выходов первого и второго счетчиков подключены соответственно ко входам первого и второго дешифраторов, другие выходы первого и второго счетчиков и выход третьего счетчика соединены со входами элементов И, выходы которых подключены ко входам элемента !

ИЛИ, вход первого триггера соединен с выходом элемента ИЛИ, а выходы подкню721 чепы к одним из выходов устройства, вхо» ды схемы сравнения соединены соответст венно с ogíèì из выходов первого тригГера и входом TpoAcTB8ð о т л и ч а ю ш е е с я тем, что с целью увеличения полноты контроля, оно содержит дополнительные элементы И и ИЛИ, второй триггер и элемент НЕ, причем входы одного из дополнительных элементов И подключены соответственно к выходам генератора тактовых импульсов и элемента НЕ, а выход соединен со входом второго триггера, вход элемента НЕ подключен к выходу элемента ИЛИ, входы

853 6 дополнительных элементов Hill соединены с выходами второго дешифратора, первые входы других дополнительных элементов

И подключены к выходам второго тригге ра, вторые входы - к выходам дополнительных элементов ИЛИ, а выходы — к другим выходам устройства, Источники информации принятые во внимание при экспертизе

1, Авторское свидетельство СССР

% 341087, кл, G 11 С 29/00, 1970.

2. Патент США % 378829, кл. 340-146.1, опубл. 1973 (прототип), Составитель В. Рудаков

Редактор H. Каменская Техред O,ЛегезаКорректор М. Шероши

Ъьказ 138 41 Тираж 662 Подписное

11НИИПИ Госуда твенного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскс наб., д. 4/5

Филиал llllll Патент, г. Ужгород, ул. Проектная, 4