Цифровой регулятор

Иллюстрации

Показать всеРеферат

ОП И Х

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Реснублик

<и>723502

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 301275(21)2309784/18-24 (51)М. Кл.2

G 05 В 11/14 с присоединением заявки М— (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 62-50 (088. 8) Опубликовано 250380; Бюллетень И9 11

Дата опубликования описания l250380 ! (72) АВТОРЫ Р. И. Батырев, В. В. МУлЯР, Б. Ф. Ва Редкий, ИЗО6 ЕтЕНИя П. В. Зобнин, О. И. Гдалин, В. И. Клочков, В. Г. Семенов и Ю. В. Гуров (71) Заявитель (54) ЦИФРОВОЙ .РЕГУЛЯТОР

Изобретение относится к системам регулирования, а именно к цифровым системам, и может быть использовано для измерения и регулирования одного или соотношения двух параметров технологического процесса.

Известны цифровые регуляторы технологических параметров, содержащие .л датчик регулируемого параметра, счет- 0 чик, регистр памяти с ключами, выходной преобразователь код-аналог и блок задания (1).

Недостатком таких регуляторов является дополнительное преобразование разности между заданным и текущим значениями регулируемого параметра перед поступлением ее в выходной преобразователь ..код-аналог, вследствие того что эта разность постпает на регистр памяти в разных кодах.

Наиболее близким к предлагаемому является цифровой регулятор, содержащий датчик и задатчик, выходы которых соединены со входами первого счетчика, соединенного с соответствующими входами блока ключей, выходы которого соединены со входами первого блока памяти, подключенного к первым входам преобразователя- код-аналог (2), 30

Недостатком такого регулятора является использование двоично-десятичного реверсивного счетчика для выполнения Ьперации вычитания действительного значения регулируемого параметра из заданного, что приводит к дополнительным преобразованиям, а, следовательно, к усложнению схемы регулятора. Кроме того, в работе реверсивного счетчика в процес— се счета наблюдаются сбои, происхо-дящие в момент смены знака разности.

Все это снижает надежность работы регулятора.

Цель изобретения — повышение на- дежности работы цифрового регулятора.

Укаэанная цель достигается тем, что в цифровом регуляторе установлены второй счетчик и последовательно соединенные индикатор нуля и второй блок памяти, первый выход которого соединен с соответствующими входами блока ключей и со вторым входом преобразователя код-аналог, а второй выход — с соответствующими входами блока ключей и второго счетчика, другой вход которого соединен с выходом датчика, а выходы соединены с соответствующими входами блока ключей, входы индикатора нуля сое723502 динены с соответствующими, выходами первого счетчика, представляющего собой нереверсивный двоичный счетчик.

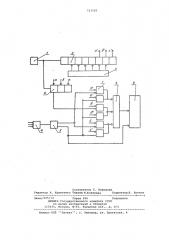

На чертеже представлена блок-схема .предлагаемого цифрового :регулятора .

Цифровой датчик 1 регулируемого параметра связан со входом первого счетчика 2, представляющего собой обычный двоичный счетчик вычитания, разряды которого связаны с эадатчиком 3. Индикатор нуля 4 первого счетчика последовательно соединен с блоком памяти 5. Вход второго счетчика б связан с цифровым датчиком 1, а выход — с блоком ключей 7, соединенным со .входами блока памяти 8, выход которого связан;с первым входом преобразователя 9 код-аналог .

На каждый вход блока памяти 8 приходится по два ключа ?, один иэ которых соединен с соответствующим разрядом первого счетчика, а другой — с тем же разрядом второго счетчика. Прямой выход блока памяти 5 соединен со входом второго счетчика 6 и с соответствующими ключами 7, входы которых соединены со вторым счетчиком. Инверсный выход блока памяти 5 соединен со вторым входом преобразователя 9 код-аналог и с соответствующими ключами 7, входы которых соединены с первым счетчиком 2.

Входы индикатора нуля 4 соединены с соответствующими выходами первого счетчика.

Устройство работает следующим образом.

В счетчике 2 формируется разность между заданным значением регулируемого параметра, вводимым н первый счетчик задатчиком 3, и его действительным значением, поступающим от датчика 1.

Если действительчое значение иэмеряемого параметра меньше заданного (положительная разность), то сигналы с последних разрядов первого счетчика (а, в, с) в прямом коде поступают на те ключи 7, которые связаны с инверсным выходом блока памяти 5.

Так как на вход блока памяти 5 не поступает управляющий сигнал, то на его прямом выходе логический сигнал отсутствует,i а на инверсном имеется сигнал, равный логической единице, разрешающий работу ключей 7, соединеннЫх с разрядами первОго счетчика 2, Бйгли действительное значение регу" лируемого парамет больше заданного значения (отрицательная разность), то в момент, когда первый счетчик 2 занимает нулевое состояние, срабатывает индикатор нуля 4 первого счетчика, который переводит блок памяти

5 в противоположное состояние, когда на его прямом выходе появляется логическая единица, разрешающая работу

Формула изобретения

50 датчика, а выходы — c соответствующими входами блока ключей, входы ин55 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 283712, кл. G 05 В 11/14, 0704Ь9.

5

25 второго счетчика 6 и тех ключей 7, которые связаны с разрядами этого счетчика (а б с) . Второй счетчик б представляет собой обычный двоичный суммирующий счетчик, в котором накаплинается остаток отрицательной разности в прямом коде, количество разрядов второго счетчика б значительно меньше количества разрядов первого счетчика 2 (поскольку разность между заданным и действительным значением регулируемого параметра — величина небольшая) и выбирается в зависимости от требований, предъявляемых к точности регулирования.

Сигналы от блока ключей 7 через блок памяти 8 поступают в выходной преобразователь 9 код-аналог, который управляет исполнительным механизмом системы регулирования.

Знак выходной аналоговой величины регулятора определяется блоком памяти 5, подающим знаковый сигнал на вход преобраэователя 9 код-аналог .

Применение предлагаемого устройства позволяет повысить надежность его работы.

Цифровой регулятор, содержащий датчик и задатчик, выходы которых соединены со входами первого счетчика, соединенного с соответствующими входами блока ключей, выходы которого соединены со входами первого блока памяти, подключенного к первым входам преобразователя код-аналог, отличающийся тем, что, с целью повышения надежности регулятора, в нем установлены второй счетчик и последовательно соединенные индикатор нуля и второй блок памяти,t первый выход которого соединен с соответствующими входами блока ключей и со вторым входом преобразователя код-аналог, а второй выход— с соответствующими входами блока ключей и второго c÷åò÷èêà, другой вход которого соединен с выходом дикатора нуля соединены с соответствующими выходами первого счетчика.

2. Круг Е. К., Диличенский С. Н.

Принципы построения одноканальных цифровых регуляторов . М ., Сов . радио, 1969, с. 161-163 (прототип) .

723502

Составитель Г. Нефедова

Редактор A. Кравченко Техред Н.Ковалева Корректор В. Бутяга

Заказ 925/12 Тираж 956 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Филиал ППП Патент, r Ужгород, ул. Проектная, 4