Преобразователь двоичной дроби в двоично-десятичную дробь

Иллюстрации

Показать всеРеферат

(72) Автор изобретения

В. И. Омельченко

Таганрогский радиотехнический институт

В. Д. Калмыкова (7!) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОЙ ДРОБИ

В ДВОИЧНОДЕСЯТИЧНУЮ LlPOBb

Изобретение относится к автоматике н вычислительной технике и может быть использовано при построении устройств, осуществляющих двоично-десятичное преобразование информации.

Известен двоично-десятичный преобразователь, содержащий сумматор, регистр сдвига, блок управления и элемент задержки $1) . Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности и схемному решению является преобразовател, содержащий регистр сдвига, первый сумматор, первый элемент задержки, два элемента И и блок управления, первый и второй выходы которого соответственно соединены с первыми входами первого и второго элементов И, выход первого элемента И соединен с первым входом регистра сдвига, второй вход которого соединен с информационной шиной преобразовачеля, выход регистра сдвига соединен с первым входом первого сумматораи через первый элемент задержки - ca вторым входом первого сумматора 21

Недостатком этого преобразователя является, относительно низкое быстроцейс твне.

Цель изобретения состоит и увеличении скорости преобразования.

Это достигается за счет выполнения умножения на сто и одновременного получения двух десятичных разрядов резуль-, тата. Для этого предлагаемый преобразователь содержит второй сумматор, второй элемент задержки, коммутатор и блок памяти, первый вход которого соединен с третьим выходом блока управления, второй вход блока памяти через коммутатор соединен с выходом второго элемента И, а выход блока памяти соединен с выходной шиной преобразователя, выход второго сумматора соединен со вторыми входами первого и второго элементов И, первый вход второго сумматора соединен с выходом первого сумматора, а второй вход второго сумматора че3 7235 рез второй элемент задержки соединен с выходом первого элемента задержки.

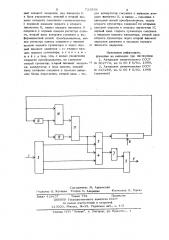

На чертеже показана функциональная схема предлагаемого преобразователя, на которой приняты следующие обозначения: управляющая шина 1, блок 2 управления, первый и второй элементы И 3,4, регистр 5 сдвига, информационная шина 6, коммутатор 7, блок 8 памяти, выходная шина 9, первый и второй (двоичные) сум- to маторы 10, 11, первый и второй элементы задержки 12, 13. Управляющая шина

1 необходима для подачи сигнала пуска на вход блока 2 управления, обеспечиваклцего работу всего устройства в целом. Е5

Первый выход блока управления 2 соединен с первым входом первого элемента

И 3, управляющего циркуляцией остатков во всех циклах, кроме первого. Второй выход блока управления 2 соединен с 2о первым входом второго элемента И 4, обеспечивающего прохождение старших семи разрядов произведения. Выход первого элемента И 3 соединен с первым входом регистра 5 сдвига, обеспечивающего циркуляцию и хранение находящейся в нем информации. Второй вход регистра

5 сдвига соединен с информационной шиной 6, служащей для записи исходного двоичного числа. Выход второго элемен- ЗО та И 4 соединен со входом коммутатора 7 который выбирает необходимую ячейку блока памяти 8. Блок памяти 8 хранит девяносто девять двоично-десятичных чисел (по числу комбинации двух десятич- З5 ных цифр от нуля ЕЕо девяносто девяти).

Выход блока памяти 8 подключен к выходным шинам 9, являющимся выходом устройства. Управление выдачей двух тетрад искомого числа производит блок управления 2, для чего его третий выход подключен ко второму входу блока памяти 8, Выход регистра 5 сдвига соединен с первым входом первого двоичного сумматора 10 непосредственно и через пер- 45 вый элемент задержки 12, смещающий двоичную информацию на тр и позиции в сторону старших разрядов, со вторым его входом и входом второго элемента задержки 13, смешеющего информаци1о на 50 три позиции в сторону стерших разрядов.

Выходы первого двоичного сумматора 10 и второго элемента задержки 13 соединены соответственно с первым и вторым входами второго двоичного сумматора 11, 55 выход которого соединен со вторыми входами первого и второго элемента И 3, 4, Необходимо отметить„что первый и

68 4 второй двоичные сумматоры 10, 11 совместно с первым и вторым элементами задержки 12, 13 обеспечивают умножение содержимого регистра сдвига 5 на

1100100 (сто в двоичном коле);

Преобразование осуществляется в следующей последовательности. На блок 2 управления поступает по управляющей шине 1 сигнал начала преобразования. Одновременно на регистр 5 сдвига с информационной шины 6 записывается двоичное число, подлежащее преобразованию. После этого начинается первый цикл преобразования. При этом содержимое регистре 5 сдвига последовательным кодом поступает на первый вход первого двоичного сумматора 10, а на второй вход — со сдвигом на три разряда. С выхода первого двои.ного сумматора 10 коды поступают ЕЕа первый вход второго десятичного сумматора 11, суммируясь c сопержимым регистра 5 сдвига, смещенным не пять позиций в сторону старших разрядов, поступающие на второй его вход с выхода второго элемента задержки 13.

Таки м образом, пр о извод итс я умножениепе двоичного числа на сто косвенным путем (путем сдвигов и сложений). При этом младшие разряды произведения (остаток) через первый элемент И 3 записываются в регистр -5 сдвига r первого по (n -2) ой разряды, à две его младших разряда необходимо установить в нулевое состояние. Старшие семь разрядов произведения через второй элемент И 4 записываются на коммутатор 7. В следующем такте производится выбор соответствуюш и пары тетрад из блока 8 памяти, поступающей EI8 выходную шину 9, являющуюся выходом преобразователя. Не этом первый цикл преобразования заканчивееп=я. В последующих циклах процесс умножения на сто, выделения старших семи разрядов произведения и остатков и выбор соответствующей пары тетред повтор яетс я.

Таким образом, за один цикл преобразования получается две разряда выходного коде, что позволяет в два реза повысить скорость преобразования.

Формула изобре те ния

Преобразователь двоичной дроби в щзоично-десятичную дробь, содержащий регистр сдвиге, первый сумматор, пер5 7 235 вый элемент задержки, два элемента И и блок управления, первый и второй выходы которого соединены соответственно с первыми входами первого и второго элементов И, выход первого элемента И соединен с первым входом регистра сдвига, второй вход которого соединен с информационной шиной преобразователя, выход регистра сдвига соединен с первым входом первого сумматора и через пер- io вый элемент задержки — co вторым входом первого сумматора, о т л и ч а ю— шийся тем, что, с целью увеличения скорости преобразования, он содержит второй сумматор, второй элемент задерж- 5 ки, коммутатор и блок памяти, первый вход которого соединен с третьим выходом блока управления, второй вход — че68 6 рез коммутатор соединен с выходом второго элемента И, а выход — соединен с выходной шиной преобразователя, выход второго сумматора соединен со вторыми входами первого и второго элементов И, первый вход второго сумматора соединен с выходом первого сумматора, второй вход второго сумматора через второй элемент задержки соединен с выходом первого элемента задержки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

_#_s 302774, кл. 6 06 F 5/02, 1969.

2. Авторское свидетельство СССР

J4ÿ 226258, кл. G 06 F 5/02, 1968 (прототип) Составитель М. Аршавский

Редактор Н. Козлова Техред О. Андрейко Корректор И. Муска

Заказ 429/37 Тираж 751 Под пис ное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППГ! Патент, г. Ужгород, ул. Пролактин, 1