Устройство для сдвига

Иллюстрации

Показать всеРеферат

Союз Советски к

Социалистических

Республик (!1172357О (61) Дополнительное к авт. свид-ву— (22) Заявлено 03.03.75 (21) 2109738/18-24 (51)M. Кл. (3 06 F 7/39 с присоединением заявки .%

Гооудоротееииый комитет

СССР (23) Приоритет по делам изобретений и открытий

Опубликовано 25.03.80. Бюллетень ¹ 11

Дата опубликования описания 25.03.80 (53) УДК 681.3 (088.8) (72) Автор изобретения

3. С. Кузин

Ленинградское высшее инженерное морское училище им. адм. С. О. Макарова (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СДВИГА

Изобретение относится к цифровой вычислительной технике и может являться как составной частью арифметикологического устройства цифровой вычислительной машины, так и выполнять функции регистра сдвига в дискретных устройствах автоматики.

Известно устройство последовательного сдвига информации, выполненное на потенциальных логических элементах и содержащее по три триггера в каждом разряде (1). Недостаток устроиства — неэкономичное использование обоIO рудования.

Наиболее близким к предлагаемому является устройство для сдвига, содержащее основной и вспомогательный и-разрядные регистры памяти, триггер управления, шины синхронизации и упIS равления записью и сдвигом, причем выходы разрядов вспомогательного регистра подключе ны к информационным входам одноименных разрядов основного регистра памяти, выход

М

i-ro ((i = 1 (n — 2) ) разряда основного регистра памяти подключен к информационному входу (i+ 2)-го разряда вспомогательного регистра памяти, синхронизирующие входы всех разрядов основного регистра памяти и счетный вход триггера управления подключены к шине управления записью в основной регистр памяти (2).

Недостатком известного устройства также является неэкономичное использование оборудования.

Цель изобретения — упрощение устройства.

Указанная цель достигается тем, что устройство соцержит логический блок последовательной записи числа, состоящий из двух элементов

И, логический блок последовательной выдачи числа, состоящий из двух элементов И, выходы которых подключены ко входам элемента

ИЛИ, и коммутатор сигналов записи и сдвига, состоящий из трех элементов И и двух элементов ИЛИ, причем первые входы элементов

ИЛИ в коммутаторе сигналов записи и сдвига подключены к выходам соответственно первого и второго элементов И, а вторые входы — к выходу третьего элемента И, шина синхронизации сигналов записи и сдвига подключена к первым входам элементов И коммутатора сигналов записи и сдвига, шина управления сдвигом на один разряд — ко вторым входам пер723570

55

3 вого и второго элементов И коммутатора сигналов записи и сдвига и к первым входам элементов И в логическом блоке последовательной записи числа, шина управления сдвигом на два разряда подключена ко второму входу

5 третьего элемента И в коммутаторе сигналов записи и сдвига, нулевой выход триггера управления подключен к третьему входу второго элемента И в коммутаторе сигналов записи и сдвига, второму входу первого элемента И в логическом блоке последовательной записи числа и первому входу первого элемента И в логическом блоке последовательной выдачи числа, единичный выход триггера управления подключен к третьему входу первого элемента И в коммутаторе сигналов записи и сдвига, вто: рому входу второго элемента И в логическом блоке последовательной записи числа и первому входу второго элемента И в логическом блоке последовательной выдачи числа, третьи входы элементов И в логическом блоке последовательной записи числа подключены к информационному входу устройства, выход первого элемен та И вЂ” к информационному входу второго, а выход второго элемента И вЂ” к информационно- 25 му входу первого разряда вспомогательного регистра памяти, выходы первого и второго элементов ИЛИ в коммутаторе сигналов записи и сдвига подключены к синхронизирующим входам соответственно нечетных и четных разрядов вспомогательного регистра памяти, выходы четного и нечетного разрядов с наибольшими номерами в основном регистре памяти подключены ко вторым входам соответственно первого и второго элементов И в логическом блоке последовательной выдачи числа, выход элемента ИЛИ в блоке последовательной выдачи числа подключен к информационному выходу устройства.

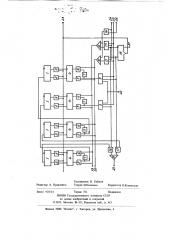

На чертеже схематически изображено четырех 4о разрядное устройство сдвига без шин установки в ноль и без схем параллельной записи нумерации разрядов справа налево.

Устройство содержит основной регистр, собранный из триггеров 1 и логических элементов 45

И 2, 3 установки триггера в единичное и нулевое состояние; вспомогательный регистр, соб-. ранный из триггеров 4 с логическими элементами И 5, 6 и НЕ 7 парафазной записи инфор-. мации; блок последовательной записи числа из логических элементов И 8, 9; коммутатор сигналов. записи и сдвига, собранный из двух элементов ИЛИ 10, 12 и трех элементов И 11, 13, 14; блок последовательной выдачи, числа, собранный иэ одного логического элемента

ИЛИ 15 и двух элементов И 16, 17; триггер

18 управления; шины 19 и 20 синхронизации нарафазной записи и сдвига нечетных и четных разрядов (или четных и нечетных при и-нечет4 ном); информационный выход 21 и вход 22 устройства; шину 23 управления записью в основной регистр памяти и в триггер управления; шину 24 синхронизации сигналов записи и сдвига; шины 25 и 26 управления сдвигом на один и два разряда соответственно; и вход 27 установки триггера управления в ноль.

Изображенное на чертеже устройство содержит только цепи параллельного сдвига на два разряда, однако они могут быть использованы и для последовательной записи и выдачи информации с шагом на один разряд.

Устройство работает следующим образом.

При выполнении операции умножения на два разряда с анализом множителя в старших разрядах на шину 26 подается сигнал разрешения сдвига на два разряда. Командный импульс сдвига подается на шину 24 и проходит через элементы И 14, ИЛИ 10 и ИЛИ 12, осуществляя сдвиг на два разряда одновременно четных и нечетных разрядов. В первый и второй младшие разряды вспомогательного регистра записываются нули. По второму временному такту сдвинутая информация переписывается в основной регистр импульсом записи, поданным на шину 23.

При выполнении операции поразрядного деления частное записывается последовательно в регистр и продвигается в сторону старших разрядов со сдвигом на один разряд. Для последовательной записи частного в регистр подается разрешающий сигнал сдвига на один разряд на шину 25, Триггер управления 18 устанавливается в исходное нулевое состояние подачей сигнала на вход 27. Частное подается на информационный вход устройства 22.

Учитывая исходное состояние триггера управления 18, первоначально вырабатывается сигнал записи и сдвига для четных (нечетных) разрядов, т. е. во второй разряд записывается старший разряд частного. По второму временному такту, поступающему на шину 23, происходит перепись информации в основной регистр, а триггер управления переключается по счетному входу в единичное состояние. В следующий цикл обработки информации вырабатывается сигнал записи и сдвига для нечетных разрядов, т. е. второй старший разряд частного записывается в первый разряд устройства.

В третьем цикле происходит сдвиг четных разрядов влево на два разряда (в описываемом примере второй разряд переписывается в четвертый) и одновременно записывается очередной разряд частного во второй разряд устройства.

В четвертом цикле происходит сдвиг нечетных разрядов (т. е. первый разряд переписывается в третий) и одновременно записывается

723570 четвертый старший разряд частного в первый разряд устройства.

Таким образом за и двухтактных циклов частное записывается в и-разрядный регистр.

Для последовательной выдачи числа триггер управления 18 устанавливается в исходное нулевое состояние, что обеспечивает выдачу числа, начиная со старших разрядов. Во втором цикле к блоку последовательной выдачи подключается второй старший разряд регистра. Та- 10 ким образом, на информационном выходе устройства 22 формируется последовательный код исла.

Если устройство содержит нечетное количество разрядов, то потенциальные входы логических элементов И 11 и И 13 подключают соответственно к нулевому и единичному входам триггера управления 18, что обеспечивает работоспособность устройства, при этом шины и 20 меняют свое название на противоположное. о

Предлагаемые схемные соединения в устройстве сдвига позволяют отказаться от цепей сдвига на один разряд, т. е. логическая схема сдвига информации упрощается в два раза, кро25 ме того расширяются функциональные возможности цепей сдвига и повышается быстродействие по сравнению с последовательным регистром сдвига множителя.

Формула изобретения

Устройство для сдвига, содержащее основной и вспомогательный и-разрядные регистры памяти, триггер управления, шины синхронизации и управления записью и сдвигом, причем выходы

40 разрядов вспомогательного регистра памяти подключены к информационным входам одноименных разрядов основного регистра памяти, выход i-го (i = 1 — (n — 2)) разряда основного ре. гистра памяти подключен к информационному

45 входу (i +2)-го разряда вспомогательного регистра памяти, синхронизирующие входы всех разрядов основного регистра памяти и счетный вход триггера управления подключены к шине управления записью в основной регистр памя50 ти, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит логический блок последовательной записи числа, состоящий из двух элементов И, логический блок последовательной выдачи числа, состоящий из

55 двух элементов И, выходы которых подключены ко входам элемента ИЛИ, и коммутатор сигналов записи и сдвига, состоящий из трех элементов И и двух элементов ИЛИ, причем первые входы элементов ИЛИ в коммутаторе сигналов записи и сдвига подключены к выходам соответственно первого и второго элементов И, а вторые входы — к выходу третьего элемента И, шина синхронизации сигналов записи и сдвига подключена к первым входам элементов И коммутатора сигналов записи и сдвига, шина управления сдвигом иа один разряд — ко вторым входам первого и второго элементов И коммутатора сигналов записи и сдвига и к первым входам элементов И в логическом блоке последовательной записи числа, шина управления сдвигом на два разряда подключена ко второму входу третьего элемента

И в коммутаторе сигналов записи и сдвига, ну левой выход триггера управления подключен к третьему входу второго элемента И в коммутаторе сигналов записи н сдвига, второму входу первого элемента И в логическом блоке последовательной записи числа и первому входу первого элемента И в логическом блоке последовательной выдачи числа, единичный выход,триггСра управления подключен к третьему входу первого элемента И в коммутаторе сигналов запаса и сдвига, второму входу второго элемента И в логическом блоке последовательной записи числа и первому входу второго элемента

И в логическом блоке последовательной выдачи числа, третьи входы элементов И в логическом блоке последовательной записи числа подключены к информационному входу устройства, выход первого элемента И вЂ” к информационному входу второго, а выход второго элемента И вЂ” к информационному входу первого разряда вспомогательного регистра памяти, выходы первого и второго элементов ИЛИ в коммутаторе сигналов записи и сдвига подключены к синхронизирующим входам соответственно нечетных и четных разрядов вспомогательного регистра памяти, выходы четного и нечетного разрядов с наибольшими номерами в основном регистре памяти подключены ко вторым входам соответственно первого и второго элементов И в логическом блоке последовательной выдачи числа, выход элемента ИЛИ в блоке последовательной выдачи числа подключен к информационному выходу устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р 396719, кл. G 11 С 19/00, 05.01.71.

2. Авторское свидетельство СССР No 337825, кл. G 11 С 19/00, 07.01.71 (прототип).

Составитель В. Байков

Редактор А. Кравченко Техред М.Келемеш Корректор О.Ковинская

Заказ 928/14 Тираж 751 Подписное

1ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4