Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

"Л

О П И б"-"А Н- И Е 723596

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Реслублнк

4i"

ЪЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (5I)M. Кл. (22) Заявлено 23.01.78 (21) 2572873/18-24

G 06 G 7/161 с присоединением заявки .%—

Государстввииый комитет (23) Приоритет

Опубликовано 25.03.80. Бюллетень ¹ 11

Ilo делам изооретеиий и открытий (53) УДК 681.335 (088.8) Дата опубликования описания 25.03.80 (72) Автор изобретения

А. Г. Афанасьев (71) Заявитель (54) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к аналоговой вычислительной технике. . Известно множительно-делительное устройство, содержащее интеграторы, компаратор и запоминающий блок (1).

Недостатком его является невысокая точность измерения.

Наиболее близким к предлагаемому является устройство, содержащее первый интегратор, информационный вход которого является входом делителя устройства, а управляющий вход соединен со входом триггера, компаратор, первый вход которого соединен с выходом первого интегратора, а второй вход является входом первого сомножителя устройства, второй интегратор, выход которого соединен со входом запоминающего блока и одновибратор (2).

Недостатком этого устройства является невысокая точность измерения, обусловленная тем, что между двумя тактами деления присут- 2О ствует временной интервал, необходимый для сбрасывания на нуль напряжения первого интегратора. Так как этот временной интервал входит в результат умножения — деления, то выходное напряжение на выходе устройства получается больше истинного на величину, пропорциональную этому временному интервалу. Точнее, напряжение, запоминающееся в запомина2У ющем блоке, равно О=((4(y,,х + Г) t õ где Т вЂ” временной интервал, необходимый для сбрасывания на нуль напряжения первого интегратора, т.е. результат вычисления имеет ошибку Ь0 = K2Z Т. Это особенно сказывается т при увеличении быстродействия устройства.

Цель изобретения — повышение точности при увеличении быстродействия.

Эта цель достигается тем, что в устройство содержащее первый интегратор, компаратер, второй интегратор, триггер, одновибратор и запоминающий блок, причем информационный вход первого интегратора является входом делителя устройства, а управляющий вход соединен со входом триггера, выход первого интегратора подключен к одному из входов компаратора, второй вход которого является входом первого сомножителя, выход второго интегратора подключен ко входу запоминающе723596

Кг ZY

К,-Х гк .г:т

К, Х го блока, дополнитель.<о введены два элемента И и ключ, информационный вход которого является входом второго сомножителя, выход соединен со входом второго интегратора, а управляющий вход подключен к выходу первого элемента И. Выход второго элемента И подключен к управляющим входам второго интегратора и запоминающего блока. Выход компаратора соединен со входом одновибратора, выход которого подключен к первым вхо- 10 дам обоих элементов И, вторые входы которых подключены к выходам триггера.

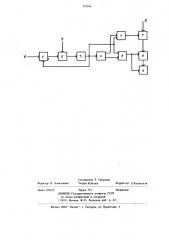

На чертеже, приведена функциональная схема устройства.

Устройство содержит первый интегратор 1, 15 компаратор 2, одновибратор 3, триггер 4, первый элемент И 5, второй элемент И 6, ключ 7; второй интегратор 8, запоминающий блок 9.

Устройство работает следующим образом.

Пусть в исходном состоянии на прямом вы- 20 ходе триггера 4 нулевой потенциал. Первый интегратор 1 пропорционально входному напряжению Х вырабатывает линейно-изменяющееся напряжение, поступающее на вход компаратора 2, нг другой вход которого подается напряжение У. 25

При достижении линейно-изменяющимся напряжением уровня напряжения У компаратор 2 срабатывает и запускает одновибратор 3, импульс с выхода которого сбрасывает на нуль первый интегратор 1. ЗО

При этом Y = К,- Х Т, где К, — коэффициент преобразования первого интегратора 1.

Т вЂ” период равенства напряжения У и линейно-изменяющегося напряжения первого интегратора 1.

Импульсы с выхода одновибратора 3 задним своим фронтом перебрасывают триггер 4, который управляет элементами И 5 и 6. Импульсы с выхода одновибратора 3 через элемент И 5 40 блокируют ключ 7, а через элемент И 6 вызывают срабатывание запоминающегося блока 9, запоминающего мгновенное значение напряжения на выходе второго интегратора 8, и,сбра- . сывание на нуль второго интегратора 8. 4>

Так как импульсы с выхода элемента И 6 возникают на каждый второй импульс с выхода одновибратора 3, а промежуточные импульсы блокируют ключ 7, то величина напряжения на выходе второго интегратора 8

$0

U„„= КгZ 2Т где Кг — коэффициент преобразования второго интегратора 8.

Напряжение, запоминающееся в запоминающем блоке 9 55

В предлагаемом устройстве. для компенсации ошибки, обусловленной наличием временного интервала, необходимого для сбрасывания на нуль напряжения первого интегратора, введен ключ 7 и устройство коммутации, построенное на базе элементов И 5 и 6, управляемое триггером 4. Ключ 7 служит для блокировки информационного входа второго интегратора на время, необходимое для сбрасывания на нуль первого интегратора в промежутке между двумя тактами деления, т.е. во время сбрасывания первого интегратора на нуль напряжение на выходе второго интегратора остается постоянным и равно

Применение предлагаемого устройства позволяет повысить точность обработки до 0,1% и выше при значительном увеличении быстродействия.

Формула изобретения

Множительно-делительное устройство, содержащее первый интегратор, компаратор, триггер, второй интегратор, одновибратор и запоминающий блок, причем информационный вход первого интегратора является входом делителя устройства, а управляющий вход соединен со входом триггера, выход первого интегратора подключен к одному из входов компаратора, второй вход которого является входом первого сомножителя, выход второго интегратора подключен ко входу запоминающего блока, о т л и ч а ю щ е е с я тем, что, с целью повышения точности при увеличении быстродействия, оно дополнительно содержит два элемента И и ключ, информационный вход которого является входом второго сомножителя, выход соединен со входом второго интегратора, а управляющий вход подключен к выходу первого элемента И, выход второго элемента И подключен к управляющим входам второго интегратора и запоминающего блока, выход компаратора соединен со входом одновибратора, выход которого подключен к первым входам обоих элементов И, вторые входы которых подключены к выходам триггера.

Источники информации, принятые во внимание при экспертизе

1. Патент США М 3564230, кл. 235 — 197, 1971.

2. Авторское свидетельство СССР Н 568056, кл. G 06 G 7/! 61, 1977 (прототип).

723596

Составитель Т. Сапунова

Техред М.Петко

КорректоР О.Ковинская

Редактор Л. Алексеенко

Заказ 929/15

Подписное

Тираж 751

UHHHHH Государственного комитета СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4