Устройство для дифференцирования частотно-импульсных сигналов

Иллюстрации

Показать всеРеферат

о и и -к н и е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

«»?23599

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (5l)M. Кл.

G 06 G 7/18 (53) ЯК С81.335 (088.8) (61) Дополнительное к авт. свид-ву— (22) Заявлено 01.03.78 (21) 2584293/1824 с присоединением заявки РЙ (23) Приоритет енвуднрстненный комнтет

СССР аа,налем нзебретеннй н атнрьпнй

Опубликовано 25.03.80. Бюллетень Р 11

Дата опубликования описания 25.03.80 (72) Автор изобретения.I0. В. Каллиников (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ДИФФЕРЕНЦИРОВАНИЯ

ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ

Изобретение относится к автоматике и вычис лительной тЕхнике, в частности к устройствам одно- и двукратного дифференцирования по времени частотно-импульсных сигналов.

Известно устройство для дифференцирования частотно-импульсных сигналов, содержащее блок управления, счетчик, делитель частоты, генератор опорной частоты, три регистра памяти, три управляемых делителя частоты, переключательный блок и блок вычитания импульсов (11. 10

Известно также частотно-импульсное диффе.ренцирующее устройство, содержащее блок управления, генератор опорной частоты, счетчики, регистры памяти, распределитель:импульсов, блок вычитания, группы элементов И и ИЛИ

15 и блоки сложения-вычитания (2).

Недостатками известных устройств являются ограниченные функциональные возможности, т. е. невозможность формировать одновременно с первой производной еще и вторую произ20 водную. по времени от частотно-импульсных сигналов.

Наиболее близким к предлагаемому является устройство для дифференцирования частотноимпульсных сигналов„содержащее три регистра памяти, информационный вход первого из которых соединен с выходом счетчика, подключенного счетным входом через делитель частоты к выходу генератора опорной частоты и к счетным входам первого и второго ; управляемых делителей частоты, а выход первого регистра памяти соединен с управляющим входом первого управляемого делителя частоты и информационным входом второго регистра памяти, выход которого подключен к управляющему входу второго управляемого делителя частоты, соединенного выходом с первым входом первого блока вычитания импульсов,выход которого подключен к счетному входу третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого делителя частоты, причем входы управления записью регистров памяти и обнуляющие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, причем выход счетчика подключен к информационному входу третьего регистра памяти, сое723599 диненного выходом с управляющим входом третьего управляемого делителя частоты, выход которого подключен к выходной шине устройства (3).

Это устройство также не обеспечивает определения второй производной по времени.

Цель изобретения — расширение функциональных возможностей устройства, С этой целью в устройство для дифферен- 10 цирования частотно-импульсных сигналов, содержащее три регистра памяти, информационный вход первого из которых соединен с выходом счетчика, подключенного счетным входом через делитель частоты к выходу генератора опорной >S частоты и к счетным входам первого и второro управляемых делителей частоты, а выход первого регистра памяти соединен с управляющим входом первого управляемого делителя частоты и информационным входом второго регистра ZO памяти, выход которого подключен к управляющему входу второго управляемого делителя частоты, соединенного выходом с первым входом первого блока вычитания импульсов, выход которого подключен к счетному входу 25 третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого делителя частоты, причем входы управления записью регистров памяти и обнуляющие входы счетчика и делителя частоты подключе- чп ны к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, дополнительно введены четвертый пятый, шестой1управляемыЕ делители частоты и второй и третий блоки вычитания импульсов, причем выход четвертого управляемого делителя частоты, подключенного счетным входом к выходу генератора опорной частоты и соединенного управляющим входом с выходом третьего регистра памяти, подключен к первому вхо- 40 ду второго блока вычитания импульсов, соединенного вторым входом с выходом второго управляемого делителя частоты и подключенного выходом к счетному входу пятого управляемого делителя частоты, управляющий вход которо- 45

ro соединен с выходом второго регистра памяти и информационным входом третьего регистра памяти, а выход пятого управляемого делитЕля частоты подключен к первому входу третьего блока вычитания импульсов, соединенного о вторым входом с выходом третьего управляемого делителя частоты и подключенного выходом к счетному входу шестого управляемого делителя частоты, управляющий вход которого соединен с выходом первого регистра памяти и с управляющим входом третьего управляемого делителя частоты, а выход шестого управляемого делителя частоты подключен к выходной шине устройства.

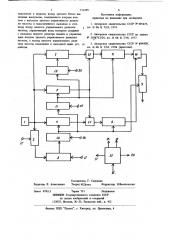

На чертеже изображена блок-схема устройства для дифференцирования частотно-импульсных сигналов.

Устройство содержит генератор 1 опорной частоты, делитель 2 частоты, счетчик 3, первый второй, третий, четвертый, пятый и шестой управляемые делители 4 — 9 частоты, первый, второй и третий регистры 10 — 12 памяти, блок 13 управления, первый, второй и третий блоки 14 — 16 вычитания импульсов. Вход блока 13 управления соединен с входной шиной устройства. Вы ходы 17 — 20 блока 13 управления подключены соответственно к входам обнуления делителя 2 и счетчика 3 и входам управления записью регистров 10 — 12 памяти. Выход генератора 1 подключен через делитель 2 частоты к счетному входу счетчика 3, а также соединен со счетными входами управляемых делителей 4, 5 и 7. Выход регистра 10, подключенного информационным входом к выходу счетчика 3, соединен с управляющими входами делителей 4, б, 9 и с информационным входом регистра 11, выход которого подключен к управляющим входам делителей 5, 8 и к информационному входу регистра 12, соединенного выходом с управляющим входом делителя 7, Входы блока 14 вычитания, подключенного выходом к счетному входу делителя 6, соединены с выходами делителей 4 и 5. Входы блока 15 вычитания соединены с выходами делителей 5 и 7, а выход его подключен к счетному входу делителя 8. Счетный вход делителя 9, соединенного выходом с выходной шиной устройства, подключен к выходу блока 1е вычитания, входы которого соединены с выходами делителей 6 и 8.

Устройство работает следующим образом.

В блоке 13 управления из последовательности импульсов входного сигнала f; формируются управляющие сигналы, определяющие последовательность работы блоков устройства. С выхода генератора 1 импульсы высокой опорной частоты fq поступают на счетные входы управляемых делителей 4, 5 и 7 частоты и вход делителя 2 частоты. В делителе 2 опорная частота делится на постоянный коэффициент К пересчета. В делителях 4, 5 и 7 опорная частота делится на переменные коэффициенты, записываемые в виде параллельного кода в соответствующие 10, 11, 12 регистры памяти.

Импульсы с выхода делителя 2 поступают на счетный вход счетчика 3, где они суммируются в промежутке времени, равном текущему периоду т„входного сигнала, формируемому путем подачи на вход 17 обнуления счетчика

3 импульсов входного сигнала fi На выходе четчика 3 в момент опроса образуется код, 5 7235 пропорциональный закончившемуся i-му периоду входного сигнала

NTI = „TI

Этот код перед обнулением счетчика 3, по сигналу с выхода 18 блока управления записывается и регистр 10 памяти. Перед записью этого кода в регистр 10 памяти, содержащийся в,регистре 10 код N>., пропорциональный -1

10 предыдущему периоду Т;1, переписывается по сигналу с выхода 19 блока управления в регистр 11 памяти. Соответственно, перед записью этого кода, содержащийся в регистре 11 код ЧТ;2, пропорциональный периоду Т; по15 сигналу с выходу 20 блока управления перепи- сывается в регистр 12 памяти. Таким образом после окончания i-го периода входной частоты в регистре 10 — код NT, в регистре 11— код N> > а в регистре 12 — код М

6-1 го

На выходах управляемых делителей 4, 5 и

7 частоты формируются соответственно частоты, пропорциональные мгновенным значениям частот f;, 1; и f; входного сигнала для середин его периодов Т;, Т;1, Т; г . На выходе блока 14 вычитания образуется разность частот с выхода делителя 4 и выхода делителя 5. Эта.разностная частота в делителе б делится на код N записанный в регистре 10 памяти. На выходе делителя 6 образуется частота 4

K (f -f ) Ка.

1-ь б т Т,. пропорциональная первои производной по вре35 мени входного сигнала в i-ом периоде. Знак этой производной определяется знаком разности частот формируемым в блоке 14 вычитания.

В блоке 15 вычитания формируется разность 4О частот с выходов делителей 5 и 7 частоты. Выходная частота блока 15 делится в делителе 8 на код йг; 1 регистра 11 памяти. На выходе делителя 8 образуется частота

К (< y — т< г1 к 1 45 о пропорциональная первой производной по времени входного сигнала в (i — 1)-ом периоде, Знак этой производной определяется знаком раз-,, ности частот, формируемым в блоке 15.

Частоты с выходов делителей 6 и 8 поступают на входы блока 16 вычитания, выходная разностная частота которого делится в делителе 9 частоты на код И;г; регистра 10 памяти.

Частота на выходе делителя 8

IP(f; — 1; g) К ° г

8, < о о

99 6 пропорциональна второй производной f; по времени входного сигнала в i-ом периоде. Знак этой производной определяется знаком разности частот, формируемым в блоке 16 вычитания.

Таким образом, устройство после окончания каждого периода входной частоты, без ухудшения быстродействия, позволяет определять кроме знака и величины первой производной также знак и величину второй производной по времени входного сигнала, т. е. обладает более широкими функциональными возможностями.

Формула изобретения

Устройство для дифференцирования частотноимпульсных сигналов, содержащее три регистра памяти, информационный вход первого иэ которых соединен с выходом счетчика, подключенного счетным входом через делитель частоты к выходу генератора опорной частоты и к счетным входам первого и второго управляемых делителей частоты, а выход первого ре-. гистра памяти соединен с управляющим входом первого управляемого делителя частоты и информационным входом второго регистра памяти, выход которого подключен к управляющему входу второго управляемого делителя частоты, соединенного выходом с первым входом первого блока вычитания импульсов, выход которого подключен к счетному входу третьего управляемого делителя частоты, а второй вход соединен с выходом первого управляемого делителя частоты, причем входы управления записью регистров памяти и обнуляющие входы счетчика и делителя частоты подключены к соответствующим выходам блока управления, соединенного входом с входной шиной устройства, отличающееся тем, что, с целью расширения функциональных воэможностей устройства, в него дополнительно введены четвертый, пятый, шестой управляемые делители частоты и второй и третий блоки вычитания импульсов, причем выход четвертого управляемого делителя частоты, подключенного счетным входом к выходу генератора опорной частоты и соединенного управляющим входом с выходом третьего регистра памяти, подключен к первому входу, второго блока вычитания импульсов, соединенного вторым входом с выходом второго управляемого делителя частоты и подключенного выходом к счетному входу пятого управляемого делителя частоты, управляющий вход которого соединен с выходом второго регистра памяти и информационным входом третьего регистра памяти, а выход пятого управляемого делителя частоты

1. Авторское свидетельство СССР %495675, кл. G 06 G 7/18, 1974.

Составитель Г. Сапунова

Редактор Л. Алексеенко Техред МЦетко Корректор Я.Веселовская

Заказ 929/15 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

7 723599 8 подключен к первому входу третьего блока вы- Источники информации, читания импульсов, соединенного вторым вхо- принятые во внимание при экспертизе дом с выходом третьего управляемого делителя.частоты и подключенного выходом к счетному входу шестого управляемого делителя частоты, управляющий вход которого соединен с выходом первого регистра памяти и управляю- 2. Авторское свидетельство СССР по заявке щим входом третьего управляемого делителя ND 2506713/24, кл. G 06 G 7/18, 1977. частоты, а выход шестого управляемого делителя частоты подключен к выходной шине уст- 0 3. Авторское свидетельство СССР М 604008, ройства. кл. G Об G 7/18, 1976 (прототип).