Логарифмический преобразователь отношения

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<и723604

©

t !

1 (61) Дополнительное к авт. свид-ву (22) Заявлено 280378 (21) 2595708/18-24 с присоединением заявки Мо (23) Приоритет

Опубликовано 250380. Бюллетень М 11

Дата опубликования описания 250380 (51}М. Хл.

G 06 G 7/24

Государственный комитет

СССР но делам изобретений и открытий (53} УДК б 81, 335,8(088.8) (72) Авторы изобретения

М.Ф. Акутин, В.А, Романов и A.Â. Широбоков (71) Заявитель (54) ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ОТНОШЕНИЯ

Изобретение относится к аналоговой и аналого-цифровой вычислительной технике, Известен логарифмический преобразователь, содержащий генератор экспоненциального напряжения, блок сравнения,.источник опорного напряжения, генератор тактовых импульсов, триггер и элемент ИЛИ (1) .

Fro недостатком является практическая невозможность осуществления логарифмического преобразования отношения двух входных напряжений во времяимпульсный сигнал.

Наиболее близким техническим решением к изобретению является логарифмический преобразователь отношения, содержащий первый и второй блоки сравнения,,ключ, источник опорного напряжения, две нС-цепи иэ параллельно включенных времяэадающего конденсатора и разрядного резистора (2).

Недостатки этого преобразователя: значительная погрешность преобразования, обусловленная наличием двух

RC-цепей и интегрированием входного напряжения; ограниченное быстродействие, обусловленное необходимостью заряда емкости RC-цепей перед каждым циклом преобразования; неоднозначность результатов преобразовани я, поскольку при отн ошени я х вход5 ных сигналов больше и меньше едини— цы могут быть получены одинаковые результаты преобразования.

Пель изобретения — увеличение быстродействия, точности и устранение неоднозначности результатов преобразования, Это достигается тем, что логарифмический преобразователь отношения, содержащий первый и второй блоки сравнения, ключ, выход которого сое15 динен с первыми входами блоков сравнения, параллельно включенные времязадающий конденсатор и разрядный резистор, соединенные общими выводами с выходом ключа и с шиной нулевого потенциала, дополнительно содержит источник. постоянного тока„ три элемента И-НЕ, два RC-триггера, D-триггер, синхрониэирующий вход которого является входом запуска преобразователя, а выход, соединен .с управляющим входом ключа, вторые входы блоков сравнения являются входами преобраэователя, выход источника пбстоянного тока соединен со вхо дом ключа, выход первого блока срав723604

;нения подключен к Я -входу первого (RS-триггера и к перьому входу первого элемента И-НЕ, второй вход которого соединен с выходом второго блока сравнения и с В-входом второго

RS-триггера, а выход — с S -входами первого и второго R5 -триггеров, с

R-входом D-триггера и с первыми входаии второго и третьего элементов

И-НЕ, выход перного RS-триггера соединен со вторым входом второго элемента И-HE выход которого является перным выходом преобразователя, выход второгî R5 -триггера соединен со вторым входом третьего элемента

И-НЕ, выход которого является вторым выходом преобразователя ° 15

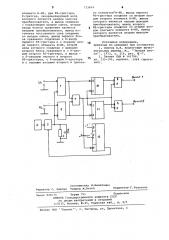

Гтруктурная схема преобразователя представлена на чертеже, Логарифмический преобразователь. отношения содержит первый 1 и второй

2 блоки сраннения, ключ 3, разрядный резистор 4, времяз адающий конденсатор 5, источник б постоянного тока, первый 7, второй 8 и третий 9 элементы H-HF, первый 10 и второй 11

R5-триггеры, 37"триггер 12, Преобразователь работает следующим образом, При подаче входных напряжений Uq и U и запускающего импульса на синхро2 низирующий вход D-триггера 12 происходит переключение D-триггера 12 и 30 открывается ключ 3, При этом источник постоянного тока б через ключ 3 заряжает времязадающий конденсатор

5. Предположим, что Ц ) Uг, тогда при достижении на конденсаторе 5 по- 35 тенциала, равного U«срабатывает второй 2 блок сравнения, на выходе которого появляется логическая 1, поступающая на второй нход элемента

7. и R-вход второго 11 RS-триггера, 40

При достижении на конденсаторе 5 потенциала, равного U, срабатывает первый 1 блок сравнения, на выходе которого также появляется логическая 1, поступающая на первый вход элемента 7 и R-вход триггера 45

10. При этом на выходе элемента 7 появляется логический 0, устанавливающий RS-триггеры 10 и 11 по входу S в состояние логической 1, а D-триггер 12 — н состояние 50 логического 0 . Переключение D-триггера 12 закрывает ключ 3 и прекращает дальнейший заряд конденсатора 5 °

При разряде конденсатора 5 на 55 сопротивление параллельно соединенного с ним разрядного резистора 4 и достижении на конденсаторе напрнже-Ь ния, равного U = ПоеХр(зс ) где U > U > Пг — напряжеййе, до о которого заряжен конденсатор 5, первый 1 блок сравнения возвращается в исходное состояние — на его выходе поянляется логический 0, В результате этого на выходе триггера

10 и элемента 7 появляются, соответственно, логический 0 и логическая 1 ° При этом на выходе логи— ческого элемента 9 появляется логический 0 . Момент переключения элемента 9 соответствует началу формирования временного интервала, являющегося результатом преобразования, Дальнейший разряд конденсатора 5 приводит к возвращению второго блока сравнения 2 в исходное состояние при достижении величины напряжения

Пг « p (- ) °

На выходе триггера 11 также устанавливается логический 0, а на выходе элемента 9 устанавливается логическая 1, Момент переключения логического элемента 9 в состояние логической 1 соответствует окончанию Формирования временного интервала, я вл яющегося результатом преобразования.

Аналогично происходит работа устройства при U< < U2. При этом формирование импульса соответствующего временного интервала происходит на выходе элемента 8, Таким образом, длительности выходных импульсов элементов 8 и 9 равны соответственно ьЬ=Rcev — (ири. u„»О ), U л (и О «О )

Благодаря применению одной RCцепи предлагаемый преобразователь имеет более высокую тбчность по сравнению с прототипом, поскольку исключаются погрешности, обусловленные неидентичностью RS-цепей, Так как в предложенном преобразователе результаты преобразования при отношениях входных сигналов больше и меньше единицы получаются на разных выходах, то исключается неоднозначность результатов преобразования, Исключение интегрирования входных сигналов и заряд конденсатора в предлагаемом преобразователе от источника постоянного тока позволяет повысить быстродействие по сравнению с прототипом.

Формул а и з о бр ет ени я

Логарифмический преобразователь отношения, содержащий первый и второй блоки сравнени я, ключ, выход которого соединен с первыми нходами блоков сравнения, параллельно включенные времязадающий, конденсатор и разрядный резистор, соединенный общими выводами с выходом ключа и с шиной нуленого потенциала, о т л ич а ю шийся тем, что, с целью увеличения быстродействия, точности и устранения неоднозначности результатов преобразования, он содержит источник постоянного тока,. три

723604 ход 1 ход 2

Составитель И. Балабошко

Редактор С. Лыжова Техред M.Ïåòêo Корректор,Г. Решетник

Заказ 929/15 Тираж 75 1 Подписное

ПНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r, ужгород, ул, Проектная, 4 элемента И-НЕ, два RS-триггера, D-триггер, синхронизирующий вход которого является входом запуска преобразователя, а выход соединен с управляющим входом ключа, вторые входы блоков сравнения являются 5 входами преобразователя, выход источника постоянного тока соединен со входом ключа, выход первого блока сравнения подключен к R-входу первого RS-триггера и к первому входу первого элемента И-НЕ, второй вход которого соединен с выходом второго блока сравнения и с R-входом второго RS-триггера, а выход с S-входами первого и второго

RS-триггеров, с R-входом D-триггера и с первьми входами второго и третьего элементов И-НЕ, выход первого

RS-триггера соединен со вторым входом второго элемента И-НЕ, выход которого является первым выходом преобразователя, выход второго

RS-триггера соединен со вторым входом третьего элемента И-НЕ, выход которого является вторым выходом преобразователя °

Источники информации, принятые во внимание при экспертизе

1. Смолов В.Б. Аналоговые вычислительные машины. M., Высшая школа, 1972, с. 216, рис. ф -7.

2. Патент США 9 161766„ кл. 235-195, опублик., 1964 (прототип),