Формирователь импульсов выборки элементов памяти

Иллюстрации

Показать всеРеферат

О П И С А И "И,Ж

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик йище)368>

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 03.11.78 (21) 2680477/18-24 с присоединением заявки .% (23) Приоритет (51)M. Кл.

G 11 С 11/40

Гееудврственньй яекятет

СССР ео делам изоорвтений н открытей

Опубликовано 25.03.80. Бюллетень .% 11 (53) УЯК. 681 327 (088.8) Дата опубликования описания 28,03.80 (72) Авторы изобретения

Н. А. Подопригора и В. Н. Дятченко

Московский институт электронной техники (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ВЫБОРКИ ЭЛЕМЕНТОВ

ПАМЯТИ Ъ

Изобретение относится к вычислительной технике и может быть использовано в запоминаюших устройствах.

Известны адресные формирователи импульсов выборки элементов памяти (1) — (3), 5

В каждом из них на выходе формирует. ся положительный импульс напряжения, который позволяет в матрице накопителя

) выбрать необходимый элемент памяти.

Однако известные устройства имеют т0 малую надежность.

Целью изобретения является повышение надежности формирователя без увеличения потребляемой мошности.

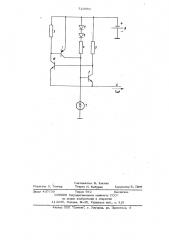

Достигается это введением в устрой15 ство дополнительного n-p-и транзистора, база которого подключена к коллектору тт-р-тт транзистора, эмиттер к шине выборки, коллектор к базе р-и-р транзи<>тора, а база и-р-тт транзистора подключена к входной шине.

Формирователь импульсов выборки ввпеж:нтов памяти содержит транзистор 1, n-p-nтранзистор 2,,резисторы 3>4> 1т

5, шина 6 выборки элементов памяти, генератор 7 тока выборки, источник

8 питания, последовательно включенные. диоды 9 смешения; дополнительный и-р-и транзистор 10.

В режиме покоя ток генератора тока выборки 7 равен нулю, Предположим, что и-р-и транзистор 2 открыт, а n-p-n транзистор 10 закрыт. Тогда за "÷åò тока коллектора транзистора 2, обусловленного током ши ы выборки 6 Ii sa„í резисторе 5 создае тся паде ние напряжения и напряжение база-эмиттер дополнительного и-р-и транзистора 10 меньше напряжения база-эмиттер транзистора 2.

Так как транзистор 10 закрыт, то и р-и-р транзистор 1 тоже закрыт. Потенциал шины выборки 6 определяется как о

О..=E,— 2U -U „-1ы R где Е; — напряжение источника питания 8;

20 — падение напряжения на диодах смешения 9; где 0 .,ц — падение напряжения на переходе база-эмиттер открытого транзистора 10; — ток базы транзистора 10; — сопротивление резистора 5.

Причем О " О,, т,е. произошло повышение потенциала шины выборки 6.

После того, как выключится генератор тока выборки 7, начнется повышение по30 мьнциала базы транзистора 2. Так как р-и-р транзистора 1 является более инерционным, чем и-р-п транзисторы 2 и 10, то его ток коллектора обеспечивает повышение потенциала базы транзистора 2 настолько, что включается транзистор 2 и выключается транзистор 10. Это приводит формирователь импульсов в первоначальное состояние, когда транзистор 2 открыт, а транзисторы 1 и 10 закрыты.

В свою очередь, потенциал шины выборки

72368

0 — падение напряжения на перехо632 де база-эмиттер открытого транзистора 2;

1 - ток базы транзистора 2;

Рд — сопротивление резистора 4 .

В момент выборки включается генератор тока выборки 7 и его ток понижает потенциал базы транзистора 2. Включается транзистор 10 и транзистор 1. Пока включен генератор тока выборки 7, тока 10 коллектора транзистора 1 недостаточно, чтобы повысить потенциал базы транзистора 2, поэтому он остается закрытым.

В данном состоянии потенциал шины вы борки элементов памяти 6 определяется.

K&K

1 изб. П 6Э4О бЮ Я

1 4 элементов памяти 6 понижается ло значения 0 = О,„

В преллагаемом устройстве р-п -.p транзистор 1 играет вспомогательную роль и его сравнительно низкое быстродействие не влияет на скорость повышения потенциала шины выборки 6.

Увеличение быстродействия формирователя достигается без увеличения потреЬ. ляемой мошности. формула изобре те ния

Формирователь импульсов выборки элементов памяти, содержащий р-п-р транзистор, база которого через первый резистор и эмиттер соединеньг с шиной питания, п-ð-и транзистор, база которого подключена к коллектору р-п-р транзистора и через последовательно соединенные второй резистор и диоды смешения к шине питания, коллектор через третий резистор подключен к шине питания, а эмиттер к шине выборки, и входную шину, о т л и ч а ю ш и и с я тем, что, с целью повышения надежности, он содержит дополнительный и -р-и транзистор, база которого подключена к коллектору и-р-и транзистора, эмиттер к шине выборки, коллектор к базе р-и-р транзистора, а база rl-p-n TpaHGHcTopa подключена к вхолной шине.

Источники информации, принятые во внимание при экспертизе

1. Патент Франции 1& 2112364, кл. 11 С 11/00, 1972.

2. Патент США М 3624620, кл. 340-173, 1972.

3. Электроника, И 9, 1974.

72368 1

Составитель В. Костин

Техред Н. Бабурка Корректор Е. Папп

Редактор Г. Гончар

Тираж 662 Под писное

11НИИПИ Государственного комитета CCCI по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4 5

Заказ 437/39

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4