Элемент с тремя состояниями

Иллюстрации

Показать всеРеферат

) /

ОПИ, ИЗОБРЕТЕНИЯ

1 с,А йи6

Союз Советских

Социалистических

Республик

<н725235

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 171078 (21) 2б74751/18-21 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 300380. Бюллетень ¹ 1 2

Дата опубликования описания 300380

Н 03 К 19/08

Государственный комитет

СССР по делам изобретений и открытий (53) УДК821.374(088.8) Ю.M. Герасимов, A.Н. Карма зинский, С. Н. Косоусав, В.Н. Филатов и В.A. Максимов (72) Авторы изобретения (71) Заявитель (54) ЭЛЕМЕНТ С ТРЕМЯ СОСТОЯНИЯМИ

Изобретение относится к вычислительной технике и электронике и может быть использовано при создании интегральных схем на МДП-транзисторах в качестве выходного ключа-усилителя для непосредственного объединения по

ИЛИ с выходными каскадами других схем. Элемент может быть использован в устройствах вывода информации статических Зу и ВИС-микропроцессоров.

Известны элементы с тремя состояниями на дополняющих МДП-транзисторах, содержащие двухтактный выходной каскад и симметричную схему управления (1).

Недостаток этих элементов заключается в значительной потребляемой мощности.

Известен элемент с тремя состояниями на дополняющих МДП-транзисторах, содержащий выМодной двухтактйый инвертор, включенный между шиной питания и общей шиной, ключевые транзисторы и и р-типа, включенные сост- 25 ветственно между первым входом выходного двухтактного инвертора и общей шиной и между шиной питания и вторым входом выходного двухтактнаго инвертора, затворы ключевых транзис-оров подключены к информационной ши1 не, инвертор, включенный между шиной питания и первым. входам выходного двухтактного инвертора, вход инвертора подключен к шине управляющего сигнала, а выход — к второму входу выходного двухтактного инвертора, и двунаправленный ключ, включенный между шиной управляющего сигнала и первым входом выходного двухтактного инвертора, затворы транзисторов двунаправленного ключа р и и-типа подключены соответственно к информационной шине и к второму входу выходного двухтактного инвертора (2).

Недостатком известного элемента является значительное потребление мощности и низкое быстродействие.

Цель изобретения — уменьшение потребляемой мощности и увеличение быстродействия.

Для достижения поставленной цели в элемент с тремя состояниями на дополняющих МДП-транзисторах, содержащий выходной двухтактный инвертор, включенный между шнной питания и общей шиной, ключевые транзисторы п и р-типа, включенные соответственно одежду первым входом выходного двух725235

1Тйктного инвертора и общей шиной и между шиной питания и вторым входом выходного двухтактного инвертора, затворы ключевых транзисторов подключены к информационной шине, и первый инвертор, включенный между шиной питания и первым входом выходного двухтактного инвертора, вход первого инн ерт ора подключе н к ши н е прям oI o управляющего сигнала, а выход — к второму входу выходного двухтактного инв ертора, вв еден в торой инв ертор, включенный между выходом первого инвертора и общей шиной, вход которого подключен к шине инверсного управляющего си гнала, а выход — к первому входу выходного днухтактного инвертора.

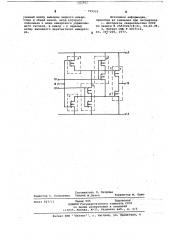

На чертеже представлена электрическая принципйальная схема элемента с тремя состояниями на дополняющих

МДП-транзисторах, Выходной днухтактный иннертор 1 включен между шиной 2 питания и общей шиной 3, ключевые транзисторы и и р-типа 4 и 5 подключены соответственно между первым входом б выходного иннертора 1 и шиной 3 и между— шиной 2 и вторым входом 4 ных одного инвертора 1, затворы транзисторов 4, 5 подключены к информационной шине

8, первый инвертор 9 включен между шиной 2 и входом. б, выход его подключен ко входу 7, а вход — к шине пря"мого управляющего сигнала 10, второй иннертор ll включен между входом

7 и шиной 3, выход его подключен ко входу б, а вход — к шине инверсного управляющего сигнала 12. Выход инвертора 1 является выходом элемента 13.

Элемент работает следующим образом.

В исходном состоянии (режим хранения для ЗУ) на шины 10 и 12 поступают собтветственно логические 0 и 1, на выходе первого инвертора 9 устанавливается логическая 1, на выходе второго иннертора 11 — логический 0 „ В результате чего, I независимо от значения сигнала на инФормационной шине 8, о6а транзистора выходного днухтактногo инвертора 1 закрыты и на его выходе устанавливается . третье состояние .

В режиме передачи информации (режим считывания для ЗУ) на шины 10 и

12 поступают соответственно логические 1 и 0, п-канальный транзистор первого иннертора 9 и р-канальный транзистор второго иннертора 11 открываются, замыкая первый и второй входы днухтактного инвертора 1. При поступлении логического 0 на информационную шину 8 открыт ключевой транзистор 5 р-типа, а второй ключевой транзистор 4-типа — закрыт. В результате чего на замкнутых входах выходного двухтактного инвертора 1 устанавливается логическая

Формула изобретения

45 Элемент с тремя состояниями на до-. полняющих МДП-транзисторах, содержащий выходной двухтактный иннерт,ор, включенный между шиной питания и общей шиной, ключевые транзисторы и и р-типа, включенные соответственно между первым входом выходного двухтактного иннертора и общей. шиной и между шиной питания и вторым нходом выходного двухтактного инвертора, затворы ключевых транзисторов подключены к информационной шине, и первый инвертор, включенный между шиной питания и первым входом выходного двухтактного инвертора, вход первого ин"вертора подключен к шине прямого уп5

t0 !

40 1, а на его выходе передаваемая информация — логический 0 . При поступлении логической 1 на шину

8 ключевой транзистор 4 открыт, а ключевой транзистор 5 закрыт, на замкнутых входах инвертора 1 устанавливается логический 0, а на его выходе передаваемая информация — логическая 1 .

Таким образом, элемент обеспечивает появление информационного сигнала на его выходе при поступлении логической 1 на шину прямого управляющего сигнала и логического 0 на шину инверсного управляющего сигнала. При противоположных значениях логических сигналов на укаэанных ши-, нах элемент находится н третьем состоянии .

Время передачи- логического 0 и 1 приблизительно одинаково, быстродействие возрастает примерно н 1,5 раза по сравнению с известной схемой.

Уменьшение потребляемой мощности обеспечивается благодаря тому, что между входами иннертора 1 включен транзистор и-типа инвертора 9 и параллельно включен транзистор р-типа инвертора 11, поэтому напряжение логической 1 поступает на вход 7 непосредственно, а на вход б через транзистор р-типа инвертора 11, а напряжение логического 0 поступает на вход б непосредственно, а на вход

7 через транзистор п-типа инвертора 9. В результате происходит более быстрое закрывание соответствующего транзистора выходного днухтактного инн ерт ора 1, что ум ен ьша ет з нач ение сквозного тока и время его протекания, а это приводит к уменьшению потребляемой мощности. равляющего сигнала, а ныхЬд — к вторсму входу выходного двухтактного инвертора, о т л.и ч а ю шийся тем, что, с целью уменьшения потребляемой мощности и увеличения быстродействия, в него. введен второй инвертор, вклю725235 ченный между выходом первого инвер-! .тора и общей шиной, вход которого подключен к шине инверсного управляющего сигнала, а выход — к первому входу выходного двухтактного инвертора.

Составитель Л. Петрова

Редак тор С . Патрушева Тех ред М. Петк о Корректор М . Пожо

Тираж 995 Подписное .

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 827/13

Филиал ППП Патент, г. Ужгород, ул. Проектйая, 10

f2

Источники и нф ормацйи, принятые во внимание при экспертизе .

1. Авторское свидетельство СССР по заявке Р 2583020/18-21, 24.02 ° 78.

2. Патент СШй 9 4037114, кл. 307-205, l)77.