Делитель частоты следования импульсов с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

:бь те («> 725238

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 0211.78 (21) 2681017/18-21 с присоединением заявки ¹â€” (51) М К„2

Н 03 К 23/00

Государственный комитет

СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 300380. Бюллетень ¹1 2

Дата опубликования описания 300380 (З) УДК 681 ° 3.055 (088.8) (72) Авторы изобретения

В.А. Артемьев, В.И. Ежелев и Л.И. Шабунин (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике и может быть использовано в дискретных системах автоматического регулирования, в измерительных устройствах ядерной радиоэлектроники, а также в сх емах. с елек ции импульс ов .

Известен делитель частоты периодических импульсов, содержащий пересчетную схему, вентили, триггер, гене-1О ратор случайных чисел и блок сравнения кодов (1).

Недостаток этого устройства — низкая надежность .

Наиболее близким по технической сущности к изобретению является делитель частоты с дробным переменным коэффициентом деления, содержащий в каждом дробном разряде управляемый делитель, выход которого соединен с единичным входом триггера соседнего старшего дробного разряда, второй вход второго вентиля соединен со входом управляемого делителя своего разряда, выход пересчетной схемы — со входом пересчетной схемы соседнего старшего дробного разряда через элемент ИЛИ, выход управляемого делителя целых с единичным входом триггера младшего дробного разряда, первый вход вентиля на входе управляемого делителя целых — с единичным выходом дополнительного триггера, нулевой вход которого связан с выходом пересчетной схемы старшего дробного разряда, а единичный — co входной шиной и вторым входом вентиля на входе управляемого делителя целых (21.

Недостатком данного устройства является его сложность и, вследствие этого, низкая надежность.

Цель изобретения — повышение надежности устройства, Цель достигается тем, что в делитель частоты следования импульсов с переменным коэффициентом деления, содержащий делитель целой части, элементы ИЛИ, триггер и делитель дробной части, введены инвертор, дешифратор нуля и формирователь импульсов, выход которого соединен со входом установки нуля делителя целой части и входом делителя дробной части, а входы — с выходами элементов ИЛЙ, первый вход первого из которых соединен с выходом делителя целой части и первым входом второго элемента ИЛИ, второй — через инвертор со входом устройства и входом делителя целой

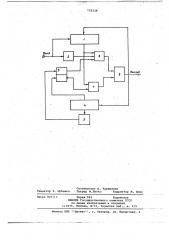

725238 части, третий — с прямым выходом трйггера, инверсный выход которого соединен со втбрым входом второго элемента ИЛИ, а единичный и нулевой входы — соответственно с выходом деЫифратора нуля и первым выходом делителя дробной части, второй выход которого соединен со входом дешифратора нуля, На чертеже изображена структурная электрическая схема .делителя частоты следбвания импульсов.

Он содержит делитель 1 целой части, инвертор 2, триггер 3, делитель

4 дробной части, дешифратор 5 нуля, первый элемент 6 ИЛИ, второй элемент 15

7 ИЛИ, формирователь 8 имйульсов.

Работа данного устройства рассматривается на примере делителя частоты следования импульсов с коэффициентам деления 24,5, 20

Переключатель делителя 1 устанавливается для получения крэффициента

24, переключатель делителя 4 в положение 5 (исходное состояние делителей 1,4 нулевое) . При этом элемент 7 закрыт запрещающим сигналом с триггера 3, а на элемент б с триггера 3 поступает сигнал разрешения.

После поступления 24 импульсов на вход делителя 1 с его выхода на вход элемента б поступает сигнал разрешения. Но с выхода элемента б импульс не следует, так как нет разрешения с инвертора 2, С поступлением на. вход . делителя 1 и инвертора 2 25-ro импульса, с выхода элемента б на формирователь 8 поступает импульс, который переводит в исходное состояние делитель 1, а делитель 4 записывает один импульс . В этом случае коэффи циент деления делителя равен 25. Пос- 40 ле того, как делитель 4 запишет пять ,импульсов (после пяти актов деления), сигналом с первого выхода этого делителя меняет свое состояние триггер 3, элемент б закрывается, а на элемент 7 с инверсного выхода триггера 3 поступает сигнал разрешения. При этом на вход формирователя 8 через элемент 7 . импульс поступает после поступления на вход делителя 1 24-го импульса.

Следовательно, остальные пять циклов деленйя из десяти происходят с коэффициентом деления 24.После досчитывания делителем 4 до исходного состояния сигналом с дешифратора 5 триггер 3 переводится в ис-, M ходите состояние и цикл деления начинается сначала . Эти процессы повто1 ряются ° При этом средний коэффициент деления составляет 24,5.

Предлагаемое устройство отличается простотой схемного построения, обладает повышенной надежностью в работе при всех возможных численных значениях коэффициента деления.

Способность устройства ав томатически изменять коэффициент деления расширяет его функциональные возможноСти. Предлагаемый делитель может быть применен для селекции импульсов по длительности, например в измерительных устройствах ядерной радиоэлектроники. Это достоинство реализуется следующим образом. При длительности входных импульсов больше длительиости импульсов формирователя

8, делитель 1 успевает дополнительно записывать один импульс после установки его в исходное состояние сигналом с формирователя 8. В этом случае коэффициент деления автоматически устанавливается равным только целой части коэффициента деления.

Формула изобретения

Делитель частоты следования импульсов с переменным коэффициентсМ деления, содержащий делитель целой части, элементы ИЛИ, триггер и делитель дробной части, о т л и ч а ю— шийся тем, что, с целью повышения надежности, в него введены инвертор, дешифратор нуля и формирователь импульсов, выход которого, соединен со входом установки нуля делителя целой части и входом делителя дробной части, а входы — с выходами элементов ИЛИ, первый вход первого из которых соединен с выходом делителя целой части и первым входом второго элемента ИЛИ, второй — через инвертор со входом устройства и входом делителя целой части, третий — с прямым выходом триггера, инверсный выход которого соединен со вторым входом второго элемента ИЛИ, а единичный и нулевОй входы — соответственно с выходом дешифратора нуля и первым выходом делителя дробной части, второй выход которого соединен со входом дешифратора нуля.

Источники информации, принятые во внимание при экспертизе

1. АВторское свидетельство СССР

Р 532964, кл. Н 03 К 23/02, 04,05.75.

2. Авторское свидетельство СССР

9 506130, кл. Н 03 К 23/00, 17,01.74..725238

Заказ 827/13

Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель A. Кружилина.

Редактор 3, Шубенко Техред М.Петко Корректор М. Поко