Устройство синхронизации по циклам

Иллюстрации

Показать всеРеферат

Сеюэ Соаетских

Социалистических

Республик!

<ц725257 ($f)+, )(л.2 (61) Дополнительное к авт. свид-ву ю 565402 (22) Заявлено 27.1077 (21) 2537577/18-09 с присоединением заявки М

Н 04 L 7/08

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 300380, Бюллетень Йо 12

Дата опубликования описания 300380 (53) УДК 621.394.

° 662 (088.8) (72) Авторы изобретения

Н.П. Пырякин, Ю.В, Леонтьевский и В.A. Денисов (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ

ИзобретЕние относится к радиотехнике и может использоваться в систе мах связи с импульсно-кодовой модуляцией в целях определения в передаче местоположения синхроимпульсов и дальнейшего осуществления синхронизации по циклам .

По основному авт. свид. Р 565402 известно устройство синхронизации по циклам, содержащее на входе формирователь тактовых импульсов и N блоков опробывания импульсных позиций с расширителями, а также делитель-распределитель и последовательно соединенные элементы И-ИЛИ, ИЛИ и элемент задержки, вход и выходы которого подключены к соответствующим входам блоков опробывания импульсных позиций, причем выход и вход первого расширителя подключены к соответствующим входам элемента И непосредственно и через накопитель, а также регистр сдвига, узел перезаписи сигналов несоответствия и элемент запрета, при ! этом выход формирователя тактовых импульсов непосредственно и через последовательно соединенные элемент- за-,. прета и делитель-распределитель подКлючен к соответствующим входам регистра сдвига, одна группа выходов которого подключена к соответствующим входам блоков опробования импульс- ных позиций, кроме первого, узла перезаписи сигналов несоответствия и элементов И-ИЛИ, а другая группа выходов — к входу. первого расширителя непосредственно, а к входам (N-1) расширителей — через элемент И, причем выходы расширителей непосредственно подключены к соответствующим входам элемента И-ИЛИ, выход которого подключен к второму входу элемента запрета, а выход узла перезаписи сигналов несоответствия подключен к дополнительному входу одного из расширителей (1)..

Однако известное устройство обладает недостаточной помехоустойчивостью, Цель изобретения — повышение номехоустойчивости устройства синхронизации по циклам.

Для достижения указанной цели в устройство синхронизации пс циклам, содержащее на входе формирователь тактовых импульсов и N блоков опробывания импульсных позиций с pacøèðèтелями, а также делитель-распредели725257 тель и последовательно соединенные элементы И-ИЛИ, ИЛИ и элемент задержки, вход и выходы которого подключены к соответствующим входам блоков опробывания импульсных позиций, причем выход и вход первого расширител подключены к соответствующим входам элемента И непосредственно и через накопитель, а также регистр сдвига, узел, перезаписи сигналов несоответствия и элемент запрета, при этом выход формирователя тактовых импульсов непосредственно и через последовательно соединенные элемент запрета и дели= тейь ="распределитель подключен к соот" ветствующим входам регистра сдвига, бд*йа группа выходов которого подклю- 15 . чена к соответствующим входам блоков опробования импульсных позиций, .кроме первого, узла перезаписи сигналов несоответствия и элементов И-ИЛИ, а другая группа выходов — к входу пер- 20 вого расширителя непосредственно, а к входам (N-1) расширителей — через элемент И, причем выходы расширителей непосредственно подключены к собтветствующим входам элемента И-ИЛИ, выход которого подключен к второму входу элемента запрета, а выход узла перезаписи сигналов несоответствия т одключен к дополнительному входу одного из расширителей, введены последовательно соединенные интегратор, фильтр нижних частот, компаратор и

"регенератор, выход которого подключен к входам N блоков опробования импульсных позиций, причем выход формирователя тактовых импульсов подключен к другому входу регенератора и входу интегратора, выход которого подключен

k другому входу компаратора, при этом на другой вход интегратора подан входной сигнал. 40

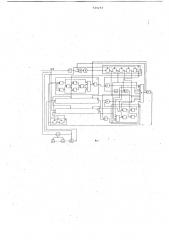

На фиг. 1 приведена структурная электрическая схема устройства; на фиг, 2 — временные диаграммы„поясняющие работу предложенного устройства. 45

Устройство синхронизации по циклам содержит формирователь 1 тактовых импульсов, блоки 2, 3 и 4 опробования импульсных позиций, расширители 5, 6 и 7, делитель-распределитель 8, . элементы И-ИЛИ 9, элемент И 10, элемент задержки 11, элемент И 12, накопитель 13, регистр 14 сдвига, узел

15 перезаписи сигналов несоответствия элемент 16 запрета, интегратор 17, фильтр 18 нижних частот, компаратор

l9 и регенератор 20.

Устройство синхронизации по циклам работает следующим образом., В режиме синхронизма входной col нал с шумом (фиг, 2а) поступает на интегратор 17, куда также поступает и сигнал с формирователя 1 тактовых импульсов (фиг. 2б), который управляет работой интегратора 17. Заряд емкости интегратора 17 осуществляется лишь в моменты времени, соответствующие высоким уровням внешнего входного сигнала и сигнала формирователя тактовых импульсов 1, следующего со скважностью, равной двум, В остальные моменты времени емкость интегратора 17 разряжена низким уровнем сигнала Формирователя 1 тактовых импульсов. Далее импульсы пилообразной формы (фиг. 2в) подаются на сигнальный вход компаратора 19, а опорное напряжение с выхода фильтра 18 нижних частот, соответствующее среднему уровню входного сигнала интегратора 17, поступает на опорный вход компаратора

19, где .происходит отсечка уровня сигнала, лежащего ниже уровня напряжения опоры (фиг. 2в) ° С выхода компаратора 19 сигнал (фиг. 2г) .поступает на регенератор 20, где восстанавливается исходная форма внешнего сигнала, но очищенная от шумов (фиг . 2д) . Стробирование сигнала в регенераторе 20 осуществляется отрицательным перепадом импульсов с формирователя 1 тактовых импульсов . С выхода регенератора 20 сформированный сигнал поступает на блоки 2, 3 и 4 опробования импульсных позиций.

Эффективность предложенного устройства заключается в повышении помехоустойчивости при достижении и поддержании условий синхронизма в устройстве синхронизации по циклам .

Формула изобретения

Устройство синхронизации по циклам

rio авт. свид. Р 565402, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные интегратор, фильтр нижних частот, компаратор и регенератор, выход которого подключен к входам N блоков опробования импульсных позиций, причем выход формирователя тактовых импульсов подключен к другому входу регенератора и входу интегратора, выход которого подключен к другому входу компаратора, при этом на другой вход интегратора подан входной сигнал.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетелЬство СССР

9 565402, кл. Н 04 L 7/08, 1974 (прототип) .

725257, о о о о

I (11!

1 ! ч ига

Составитель A. Сагадиев

Редактор П. Макаревич Техред М.Петко,, Корректор И. Муска

Закав 828/13 Тираж 729 Подписное

ЦНИИПИ Государственного ксМкитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Филиал ППП Патент, г, Ужгород, ул, Проектная, 4