Устройство для решения дифференциальных уравнений

Иллюстрации

Показать всеРеферат

пв т4фтно-т щи (есугая ф Us i H,QT, . и Щ,й, «»726543

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 110478 (21) 2603663/18-24 с присоединением заявки ¹ (23) Приоритет—

Опубликовано 050480. Бюллетень № 13

Дата опубликования описания 10.04.80.(я) . g,..2

G 06 G 7/38

Государственный комитет

СССР но делам изобретений и открыти и (53) УДК 681 333 (088.8) Ю, И. Дзибалов, A. И. Копотилов, А. Т. Лукьянов и В. И. Щербак

l (72) Авторы изобретения

Казахский ордена Трудового Красного Знамени государственный университет им. С. М. Кирова (71) Заявитель (54) УСТРОИСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ

УРАВНЕНИИ

Изобретение относится к аналоговой вычислительной технике и предназначено для автоматического нахождения решений дифференциальных уравнений в частных. производных на реэистивной сетке Либмана.

Известен сеточный электроинтегратор, содержащий автоматический потенциометр, аналоговое запоминающее устройство, выход которого подключен через сопротивление к узловой точке сетки интегратора, а вход периодичес-. ки подключается к электрическому выходу потенциометра (1).

Наиболее близким техническим решением к изобретению является устройство для решения дифференциальных уравнений, содержащее источник напряжения, R-сетку, и ячеек памяти, где п равно числу шагов разбиения области, и выходное. устройство (2) °

Недостатком известных устройств является невысокое быстродействие.

Цель изобретения — повышение быстродействия и точности устройства.

Это достигается тем, что в устройство для решения дифференциальных уравнений, содержащее источник напряжения, R-сетку, и цепочки из последовательно соединенных ячеек памяти,,введены по числу узлов R-сетки группы инверторов и группы ячеек памяти, причем выход каждого, инвертора первой группы подключен ко входу соответствующей ячейки памяти первой группы, выход которой соединен со входом соответствукщей ячейки памяти второй группы, выход которой подключен к соответствующей граничной точке R-сетки и ко входу, соответствукщему входу инвертора второй груй= пы, выход которого через цепочку иэ . последовательно соединенных ячеек памяти подключен к соответствующему выходу устройства, первый выход источника напряжения соединен с управляющими входами нечетных ячеек памяти цепочек и ячеек первой группы, управляющие входы ячеек памяти второй г >уппы и четных ячеек памяти цепочек пбдключены ко второму выходу источника напряжения, каждая узловая точка

R-сетки соединена со входом соответствующего инвертора первой группы.

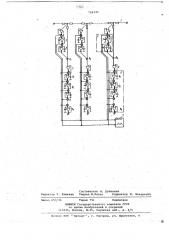

На чертеже представлена структурная схема устройства.

Оно содержит R-сетку 1, первую группу инверторов 2, первую и вторую

726543 группы ячеек памяти 3 и 4 соответст-. венно, вторую группу инверторов 5, к ячеек памяти б, -б „, источник напряжения 7, ключевой элемент 8, конденсатор 9.

Устройство работает следующим образом.

Рассмотрим и-ный узел R-сетки. В исходный момент времени ячейка памяти второй группы 4 содержит на конденсаторе 9 напряжение, соответствующее по абсолютной величине напряжению начального условия, но противоположное пд знаку. Инвертированное ячейкой памяти

- -напряжение этой величины йрисутствует на входе узла сетки А „ и на входе ячейки 6, повторенное ее инвертором 5. В узле R-сетки отработано напряжение решения на первом временном шаге. На входе ячейки 3 это напряжение повторяется через ее инвертор 2. В остальные ячейки памяти занесены нулевые 2О напряжения. С проявлением на первом выходе источника 7 первого импульса открывается ключевой элемент S ячейки памяти 3, и решение для первого вреМенного шага Записывается йа ее 2 конденсатор 9. Этим же импульсом открываются все ключевые элементы в нечетных ячейках памяти,и происходит запись информации из предыдущих им четных ячеек этой цепи. В силу нуле- ЗО вых исходных значений на всех конден саторах цепи F останутся неизменные нулевые напряжения За исключением первого, куда будет занесено Напряжение

- -начального условия со входа А„.

Второй (по времени) импульс поступает со второго выхода источника 7 и откроет ключевой элемент ячейки памяти 4 в цепи E и перепишет инвертиро-- - ванное значение напряжения решения для первого временного шага на свой 4О конденсатор. Напряжение решения для первого временного шага, будучи вторично инвертировано ячейкой памяти 4 цепи Е, окажется на входе узла Ап.

Этим же импульсом открываются все клю- чевые элементы четных ячеек памяти в цепи F.. В силу нулевых исходных значений на всех конденсаторах цепи Г останутся неизменнЫе нулевые напряжения, эа исключением первого, куда уже занесено напряжение начального условия, и втброго, куда теперь это напряжение перезапишется. фетий (по времени} импульс поступает с первого выхода источника 7 и совершает те же коммутации, что и пер-55 . вый. В результате полученное R-сеткой решение на втором временном шаге с выхода узла запишется на конденсатор 9 ячейки памяти 3, а на конденсатор 9 ячейки памяти 6 в цепи F будет занесено значение напряжения для первого временного шага, С поступлением очередных импульсов цепь E будет осуществлять циклическое получение решений, а цепь F записывать их, сохранять и, в соответствии с тактами цикла, продвигать вдоль .цепи, в конечном итоге выдавая для считывания с выхода ячейки памяти б .

Если ключевыми элементами ячеек памяти цепи F управлять импульсами, частота которых поделена на два по сравнению с импульсами, управляющими цепью Е, то полученные решения будут записываться в цепи F через одно. Выбирая степень деления частоты, можно запоминать нужные решений из просчи— тываемых. формула изобретения

Устройство для решения дифференциальных уравнений, содержащее источник напряжения, R-сетку, цепочки из последовательно соединенных ячеек памяти, о т л и ч а ю щ е е с я тем, что, с целью цовышения быстродействия и точности в устройство введены по числу узлов R-сетки группы инверторов и группы ячеек памяти, причем выход каждого инвертора первой группы подключен ко входу соответствующей ячейки памяти первой группы, выход которой соединен со входом соответствующей ячейки памяти, второй группы, выход которой подключен к соответствующей граничной точке R-сетки и к входу, соответствующему входу инвертора второй группы, выход которого через цепочку из последовательно соединенных ячеек памяти подключен к соответствующему выходу устройства, первый выход источника напряжения: соединен с управляющими входами нечетных ячеек памяти цепочек и ячеек памяти первой группы, управляющие входы ячеек памяти второй группы и четных ячеек памяти цепочек подключены ко второму выходу источника напряжения, каждая узловая точка R-сетки соединена со входом соответствующего инвертора первой группы.

Источники информации,принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 171169, кл, G 06 G 7/46, 1963.

2, Авторское свидетельство СССР

9 154733, .кл. С 06 6 7/18, 1962 (прототип) . 7 26 543

Составитель И., Дубинина

Редактор т. клюкнна техред м.пекло Корректор ю. макаренко

Заказ 653/36 Тираж 751 Подпис ное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4