Устройство для вычисления показательных функций

Иллюстрации

Показать всеРеферат

с,.

) 64"„,,, "! опис-""

Союз Советских

Социалистических

Республик (i!i 728126

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 30,12.75 (21)2308309/18-24 с присоединением заявки .% (23) Приоритет (51 ) М. Кл.

G 06 F 7/38

Гасударственный комитет

СССР. до делам изобретений и открытий

Опубликовано 15.04.80. Бюллетень М 14

Дата опубликования описания 15.04.80 (53) УДК 681.

3 25 (088.8) К. Г, Вьлков, В. И. Корнейчук, В. П. Тарасенко и О. Н. Бойчев (72) Авторы изобретения

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПОКАЗАТЕЛЬНЫХ

ФУНКЦИЙ

"=м4

Изобретение относится к области вычислительной техники.

Известно устройство для вычисления функции е", содержащее долговременное запоминающее устройство для хранения значений функций (1), Наиболее близким техническим решением к данному изобретению является устройство (21 для .вычисления показательных функций, содержащее регистр аргумента, накопитель, cocro10 ящий из и сдвигающих регистров, блок умножения, элемент И и блок управления, первый выход которого через регистр аргумента и элемент И,соединен с первым входом блока умножения и первым входом блока управле15 ния, второй выход которого соединен со вторым входом блока умножения, третий выход блока управления соединен со входами управ. ления сдвигаияцих регистров накопителя, информационнью входы которых соединены с информационными шинами устройства (21. Кро-ме того, зто устройство содержит дешифратор.

Недостатками известных устройств являются сложность,и низкая точность вычислений.

Целью изобретения является повышение точности вычислений.

Цель достигается тем, что устройство содержит и элементов И и блок выборки информации, первый и второй входы которого подсоединены соответственно к выходу регистра аргумента и четвертому выходу блока управления, а разрядные выходы сдвигающих регистров соединены с первыми входами элементов И и через блок выборки информации со входами блока умножения, вторые входы элементов И соединены с пятым выходом блока управления, а также тем, что блок выборки информации содержит Il элементов И, первые входы которых подключены к первому входу блока выборки информации, вторые — к информационным входам блока выборки, а выходы элементов И подключены к выходу блока выбор. ки; кроме того блок выборки информации содержит элементы И, многовходовый элемент

ИЛИ и коммутатор, информационные входы которого через элементы И и ИЛИ соединены с выходом блока выборки информации, вторые входы элементов И соединены с первым вхо3 72812 дом блока выборки информации, второй вход которого соединен со входом коммутатора.

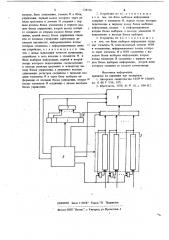

На чертеже показано предлагаемое устройство.

Оно содержит регистр аргумента 1, блок выборки информации 2, накопитель 3, группу иэ и элементов И 4, блок управления 5, блок умножения 6 и элемент И 7.

Принцип работы устройства следующий, Если необходимо вычислить а", где х=а 2к+... 10

+а 2О + a 2 +...+n 2™, n =10,11, то можем записать х L к2. с.й . ы.2.

В зависимости оТ заданного диапазона изменения аргумента Х и точности вычисления коли-15 чество разрядов для записи целой части — к и дробной части — m может быть различным (к+т=п) .

Для вычисления значения показательной функции N при заданном основании а и аргументе Х необходимо перемножить все значения à " (2j-веса всех разрядов аргумента, 2

:значение которых равно логической "1".

При х = 0101, 1001 (m=4. к=4). ъ х 0

i-w (оаЬ а-4 аа аО г а ". ,„оа ° a ° а =а а ° а .с

В накопителе 3 до начала вычисления запи- уЮ -гб саны коды чисел e, Q,..., a., а,...,а !

1ри этом в накопителе 3 хранятся мантиссы и 30 порядки этих кодов, Блок умножения 6 обрабатывает числа, записанные с плавающей запя- той, это вызвано тем, что значения степенных функций быстро изменяются.

В начале вычисления с блока управления 5 зБ в блок умножения 6 записывается код, равный единице. Это необходимо для того, чтобы при пбступлении в блок умножения 6 кода аа (2 1 I вес первого иэ исследуемых разрядов, значение которого равно логической 1 ) при умножении 4р не получился;код, равный нулю.

Устройство может работать, начиная вычисление с любого разряда аргумента. При этом информация в накопителе должна быть записана в такую последовательность, в которой произво-4 дится исследование разрядов аргумента. Зля простоты рассмотрим работу устройства, если исследование начинается либо с младшего, либо со старшего разряда аргумента.

После выполнения i-1 тактов на выходе 8 чо регйстра аргумента находится значение разряда с весом 2",если 1 < к, или разряд с весом .

2-(""), если i ) к, при условии, что работа устройства начинается со старшего разряда аргумента. Если в устройстве вычисления начинаются с младшего разряда, то на выходе 8 регистра аргумента нахоцится значение разряда с весом 2 (п — 0, при i< m нли 2 - и при 0тп.

При условии, что значение исследуемого разряда равно логической "1", блок выборки.информации 2 открывается. Значение этого разряда поступает по шине сигнала умножения в блоки управления 5 и умножения 6, Код, соответствующий этому разряду, с BblxogoB накопителя через открытую цель выборки информации 2 поступает в блок умножения 6, где умножается на содержа|цийся в нем код. По окончании операции умножения, блок управления 5 вырабатывает сигнал, который по шине сигнала сдвига информации регистра аргумента и по шине сигнала управления поступает соответственно в регистр аргумента 1, где сдвигается информация в нем на один разряд по направлению к выходу 8 регистра аргумента, и в цепь выборки информации 2, где подготавливается выбор следующего кода.

Если значение исследуемого разряда равно логическому "0", то цепь выборки информации 2 остается закрытой. По шине сигнала умножения это значение поступает в блок управления 5. Блок управления 5 сразу вырабатывает сигналы сдвига и управления. По этим сигналам происходят аналогичные процессы как и в случае, когда значение разряда равно

1 логической "l", Для того, чтобы на выходах накопителя находился нужный код, необходимо сдвигать информацию в регистрах. накопителя. По шине сигнала сдвига информации накопителя с блока управления 5 поступают сигналы, управляющие сдвигом. При сдвиге информация с выходов накопителя через схемы запрета 4, которые открыты, поступает на входы накопителя и перезаписывается, После исследования значений всех и разрядов кода аргумента Х, на выходе элемента Ч 7 есть единичный сигнал. Он поступает по шине сигнала конец операции в блок умножения 6 и блок управления 5. Сигнал конец операции означает, что в блоке умножения 6 находится код результата вычислений. Для вычисления значений степенных функций с другим основанием, например в, необходимо заменить информацию в накопителе 3, Замена производится путем подачи на входы накопителя кодов чик к-1 О сел4эа Р „. 1Р b ... Ь

t и сигнала блокировки по шине сигнала блокировки с блока управления 5, а также сигнала сдвига по шине сигнала сдвига информации накопителя. Сигнал блокировки закрывает схемы запрета 4 и перезапись информации с вы ходов накопителя на входы накопителя не производится.

Формула изобретения

1. Устройство для вычисления показательных функций, содержащее регистр аргумента, накопитель, состоящий иэ и сдвигающих ре728126

ЦНИИПИ Заказ 1138/47 Тираж 751 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

4 гистров, блок умножения, элемент И и блок управления, первый выход которого через регистр аргумента и элемент И соединен с первым входом блока умножения и первым входом блока управления, второй выход которого соединен со вторым входом блока умножения, третий выход блока управления соединен со входами управления сдвигающих регистров накопителя, информационные входы которых соединены с информационными шина- о. ми устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности вычисления устройства, в него введены п элементбв И и блок выборки информации, первый и второй входы которого подсоединены соответственно к выходу регистра аргумента и четвертому вы- ходу блока управления, а разрядные выходы сдвигающих регистров соединены с первыми входами элементов И и через блок выборки информации со входами блока умножения, вторые О входы элементов И соединены с пятым выходом блока управления.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок выборки информации . содержит и элементов И, первые входы которых подключены к первому входу блока выборки информации, вторые — к информационным входам блока выборки, а выходы элементов И подключены к выходу блока выборки.

3. Устройство по и 2, о т л и ч а ю щ е ес я тем, что блок выборки информации содержит элементы И, многовходовый элемент ИЛИ и коммутатор, информационные входы которого через элементы И и ИЛИ соединены с выходом блока выборки информации, вторые входы элементов И соединены с первым входом блока выборки информации, второй вход которого соединен со входом коммутатора.

Исто лпки информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 336669, кл. G 06 F 7/38, 1971.

2, Electronics, 1970, 43 М 10, с. 104-111.